Integrated circuit parallel testing method, device and system

A technology for judging circuits and output circuits, applied in the field of integrated circuits, which can solve the problems of limited test channels, test efficiency, and inability to achieve large-scale simultaneous/parallel comparison of units under test.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

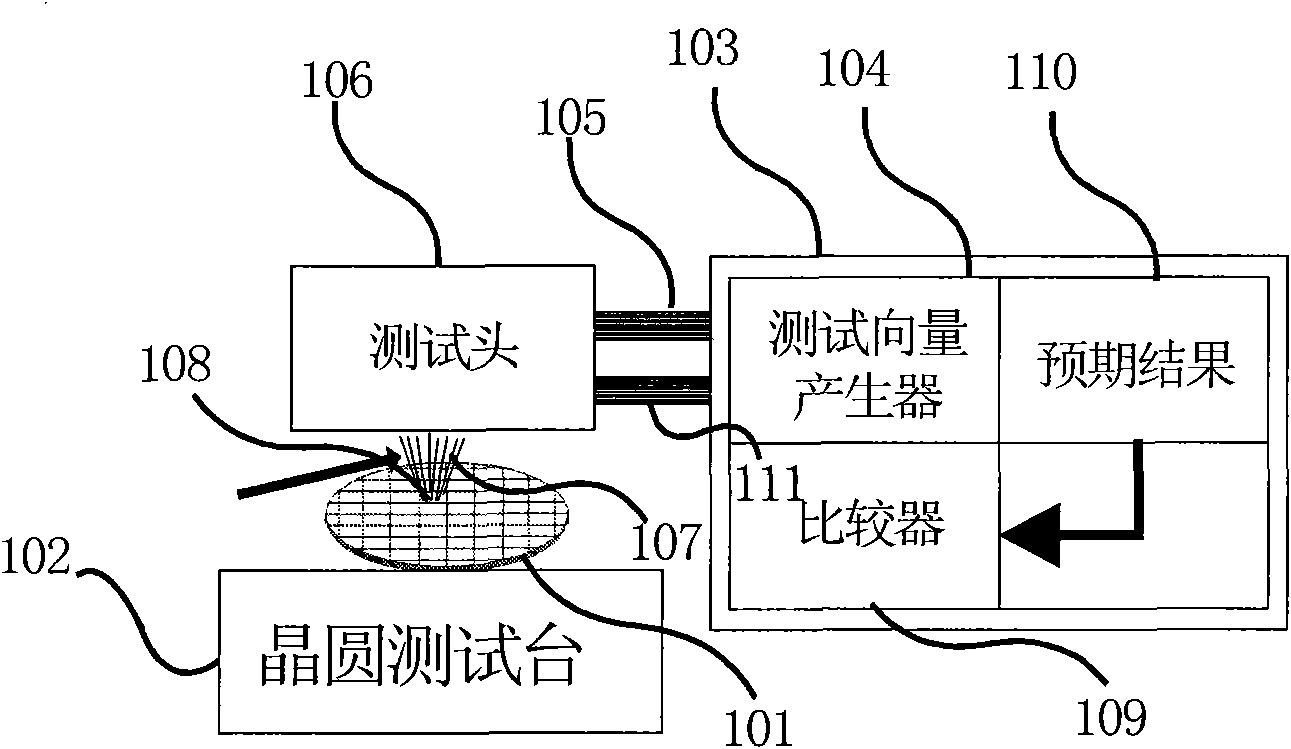

[0160] The technical idea of the present invention is that a plurality of tested integrated circuits / chips / functional chips with the same structure and function execute the same input stimulus, each of which produces operation results, and the operation results are compared with each other or with the expected results in parallel to detect failures Integrated circuit / die / functional chip.

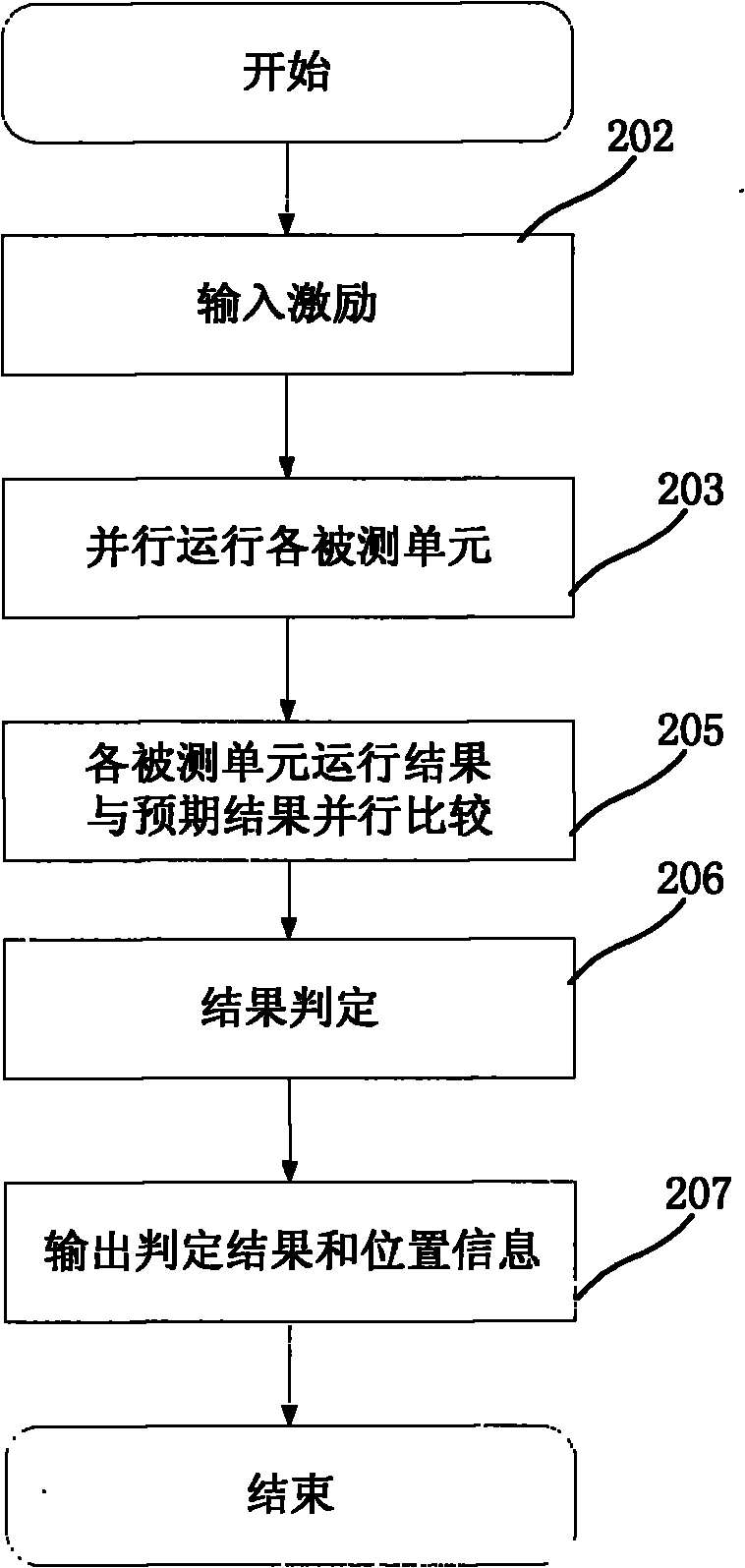

[0161] see figure 2 , figure 2 It is a flow chart of testing under the condition that the common substrate integrated circuit testing device of the present invention has expected results. The comparison device in this embodiment does not include a failure judgment function. First enter step one (202), input excitation, and then enter step two (203) to run each unit under test in parallel. Then enter step 3 (205) to sample the operation results of each unit under test, and compare them in parallel with the expected results, and record the comparison results. The number of sampling comp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More