Method and structure for enhancing write-in speed of floating body dynamic random memory cell

A technology of dynamic random access storage and writing speed, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of incompatibility, difficult manufacturing process, limited application, etc. Writing speed, the effect of increasing the longitudinal electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

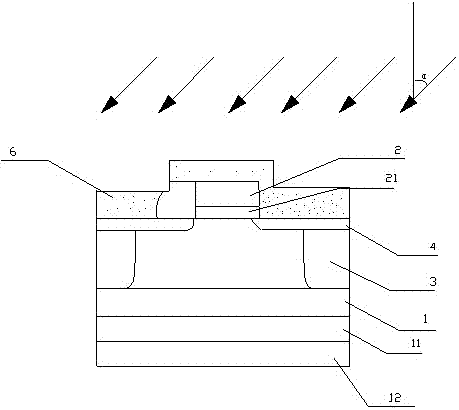

[0025] The present invention will be further described below in combination with principle diagrams and specific operation examples.

[0026] As shown in Figure 1, a kind of method of the present invention improves the writing speed of floating body DRAM unit, and it comprises the following steps:

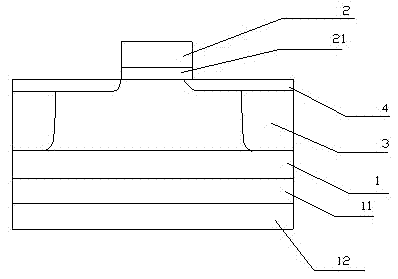

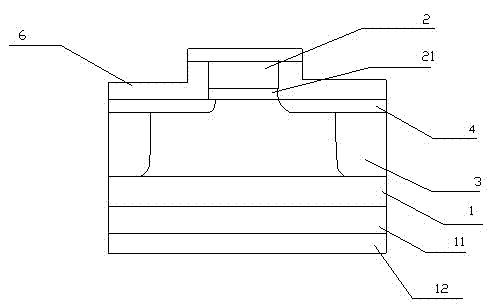

[0027] Such as Figure 1A As shown, gate 2 and shallow trench isolation trench 3 are prepared on substrate 1; lightly doped ions are implanted into substrate 1 and gate 2, and lightly doped sources are formed in the substrates on both sides of gate 2 drain 4;

[0028] In this step, the substrate 1 further includes a bottom layer 12 and an isolation layer 11 , wherein the isolation layer 11 is located between the bottom layer 12 and the substrate 1 . Preferably, the isolation layer 11 is a buried oxide layer, and the bottom layer 12 is made of silicon.

[0029] In addition, a thin oxide layer 21 is also included between the gate 2 and the substrate 1 .

[0030] Such as Figure 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com