Transverse diffusion metal oxide semiconductor (MOS) device with low on-resistance

A low on-resistance, semiconductor technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of large layout area and volume reduction, so as to improve design space, reduce on-resistance and switching loss, increase Effect of Channel Density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

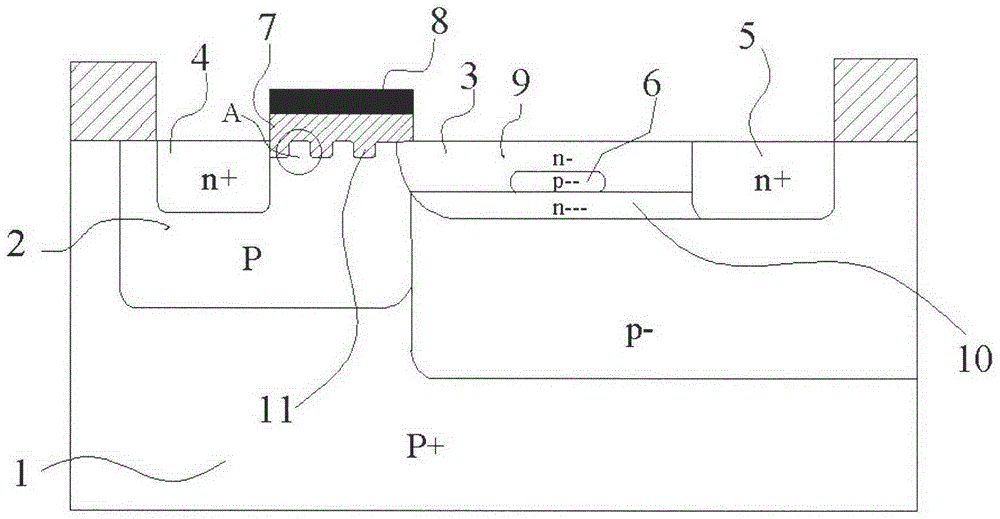

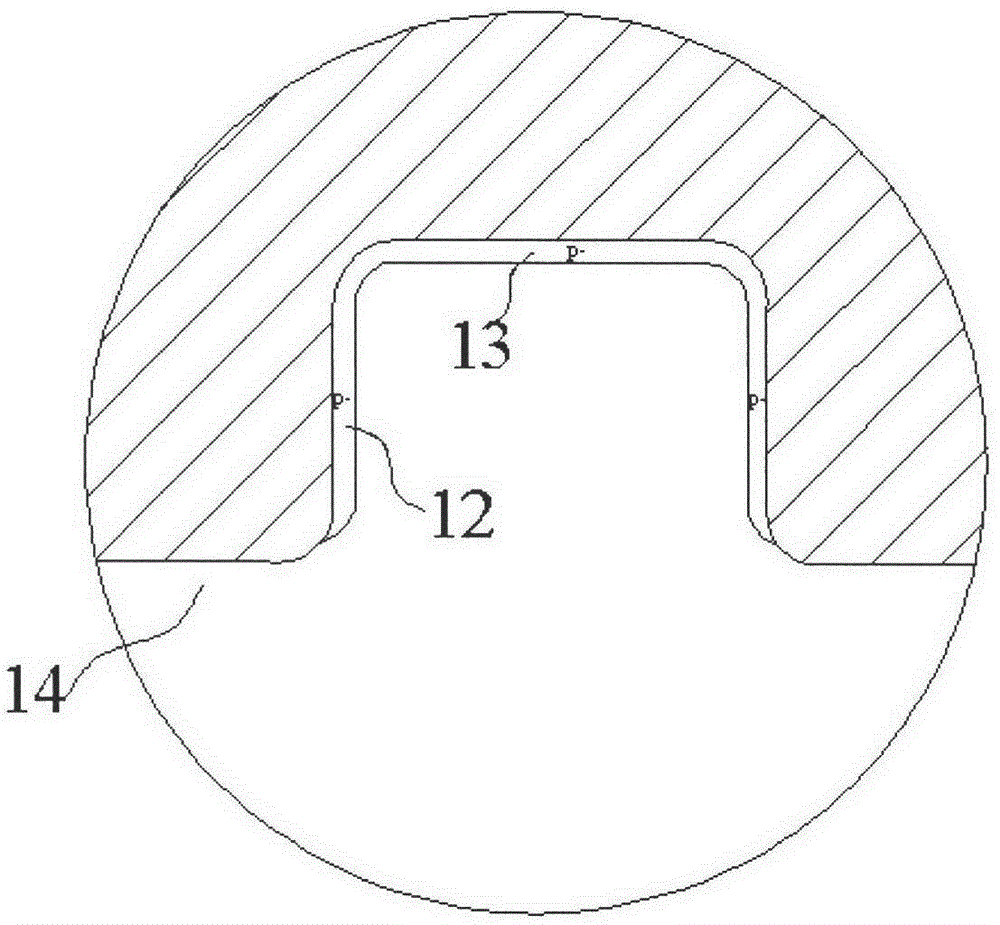

[0026] Embodiment: a kind of laterally diffused MOS semiconductor device with low on-resistance, comprising: a P-type well layer 2 and an N-type lightly doped layer 3 located in a P-type substrate layer 1, and the P-type well layer 2 and N-type Type lightly doped layers 3 are adjacent in the horizontal direction to form a PN junction, a source region 4 is located in the P-type well layer 2, a drain region 5 is located in the substrate layer 1, and a drain region 5 is located in the source region A gate oxide layer 7 is provided above the P-type well layer 2 in the region between 4 and the N-type lightly doped layer 3, and a gate region 8 is provided above the gate oxide layer 7; the source region 4 is connected to the N-type lightly doped layer At least two grooves 11 are opened between the heterogeneous layers 3 and on the upper part of the P-type well layer 2, and the etching depth of the grooves 11 is between 1 / 4 and 1 / 5 of the junction depth of the source region 4; the groo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More