Grating coupler and manufacturing method thereof

A technology of a grating coupler and a manufacturing method, which is applied to the coupling of optical waveguides, light guides, optics, etc., can solve the problem that the grating coupler is not suitable for integration in CMOS technology, the coupling efficiency of the grating coupler is difficult to improve, and the thickness of the SOI buried oxide layer is strictly required. and other problems, to achieve the effect of relaxing specification requirements, reducing dependence, and reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Such as Figure 1~5 As shown, the present embodiment provides a method for manufacturing a grating coupler, and the method at least includes the steps of:

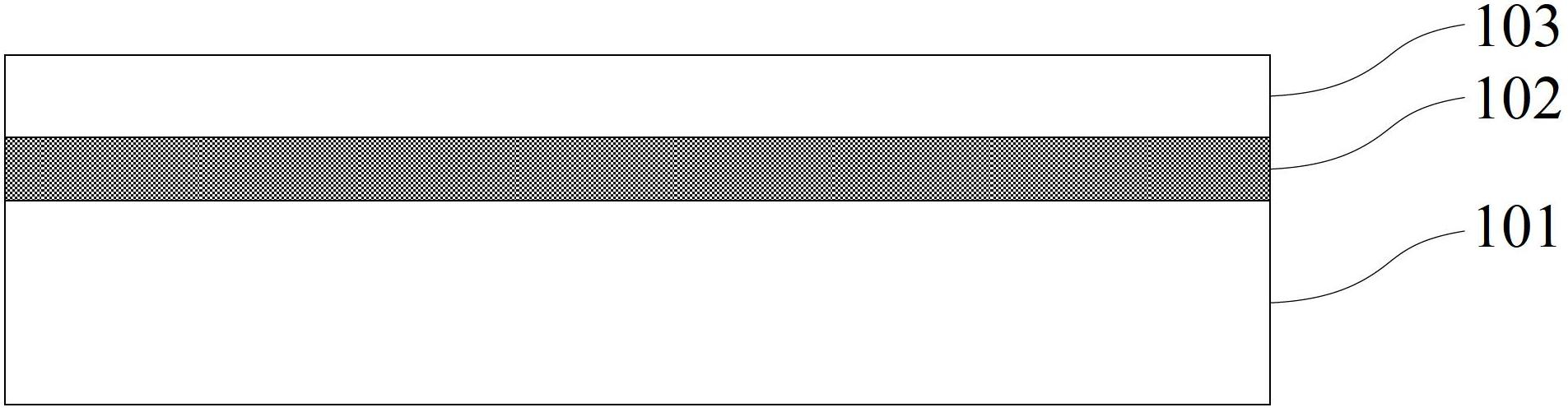

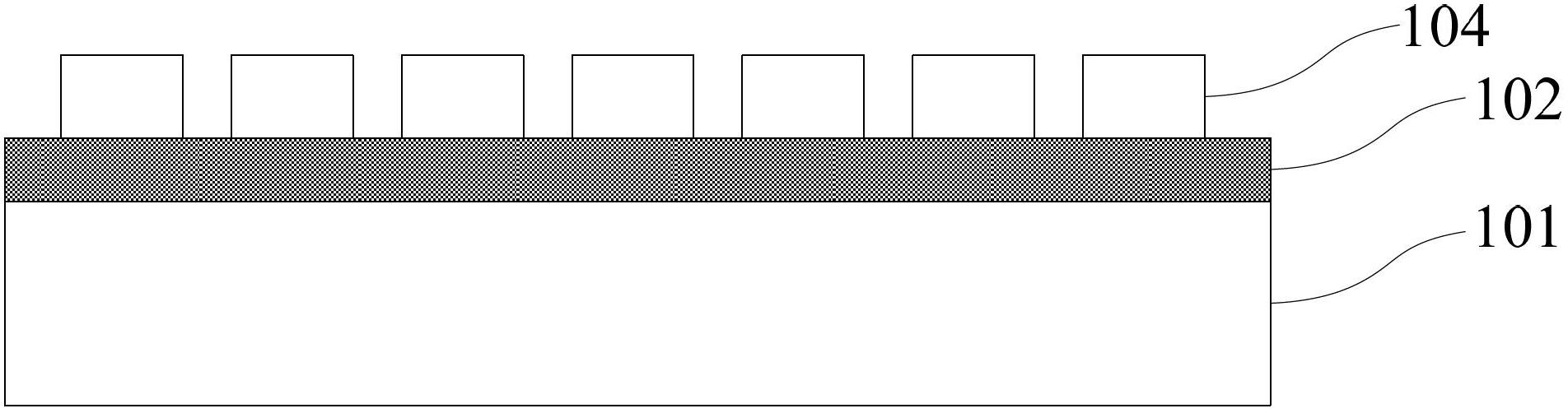

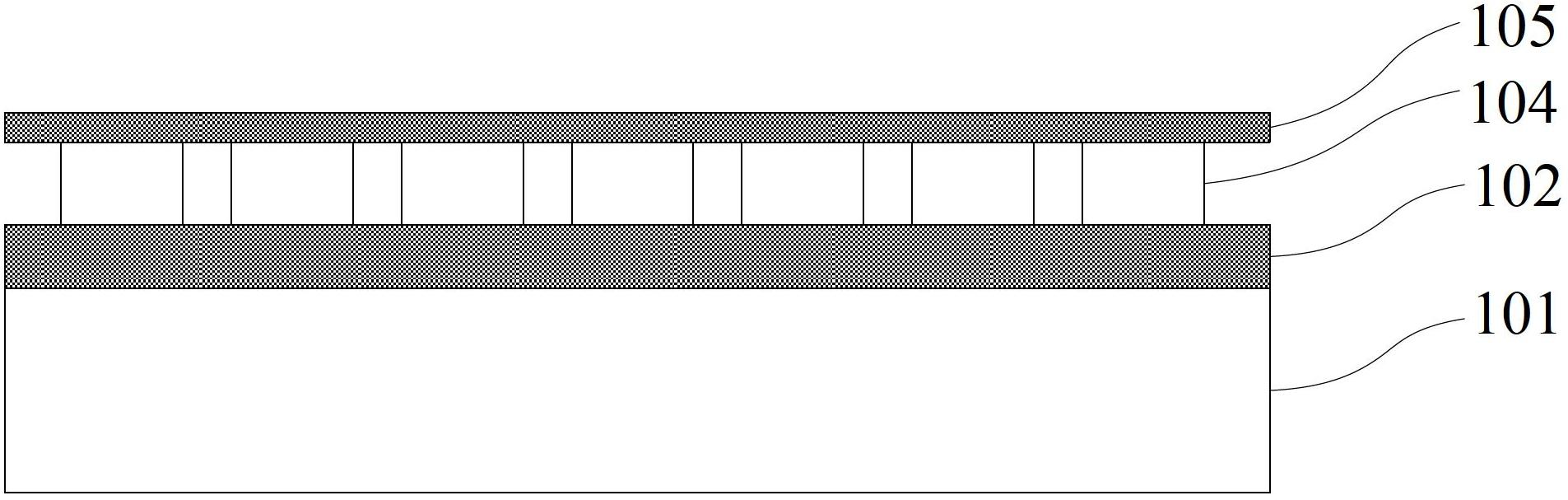

[0045] Such as Figure 1~2As shown, step 1) is first performed, providing an SOI substrate, the SOI substrate includes a back substrate 101, a buried oxide layer 102, and a top layer of silicon 103, and etching the top layer of silicon 103 to the buried oxide layer 102, A coupling grating 104 having a plurality of silicon block structures arranged at intervals and a period of 500-800 nm is formed.

[0046] The ratio of the width of the silicon block structure to the period of the coupling grating 104 is 0.7-0.99:1. In this embodiment, the ratio of the width of the silicon block structure to the period of the coupling grating 104 is 0.9:1, that is, the filling factor of the coupling grating 104 is 0.9. Specifically, if the period of the coupling grating 104 is selected as 700nm, the width of the silicon block stru...

Embodiment 2

[0062] see Figure 6~Figure 10 , as shown in the figure, this embodiment provides a method for fabricating a grating coupler, such as Figure 1~5 As shown, the present embodiment provides a method for manufacturing a grating coupler, and the method at least includes the steps of:

[0063] Such as Figure 6~7 As shown, step 1) is first performed, providing an SOI substrate, the SOI substrate includes a back substrate 101, a buried oxide layer 102, and a top layer of silicon 103, and etching the top layer of silicon 103 to the buried oxide layer 102, A coupling grating 104 with a plurality of silicon block structures arranged at intervals and a period of 500-800 nm is formed, and at least one CMOS active region 108 with shallow trench isolation grooves 109 on both sides is isolated in the top layer of silicon 103 .

[0064] In this embodiment, a pattern including etching the coupling grating 104 and one or more CMOS active regions 108 is produced in the same mask, and the top-...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More