Tri-strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SiGe HBT (Heterojunction Bipolar Transistor) and preparation method

An integrated device, three-strain technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of limitation, low mobility of Si material carrier materials, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

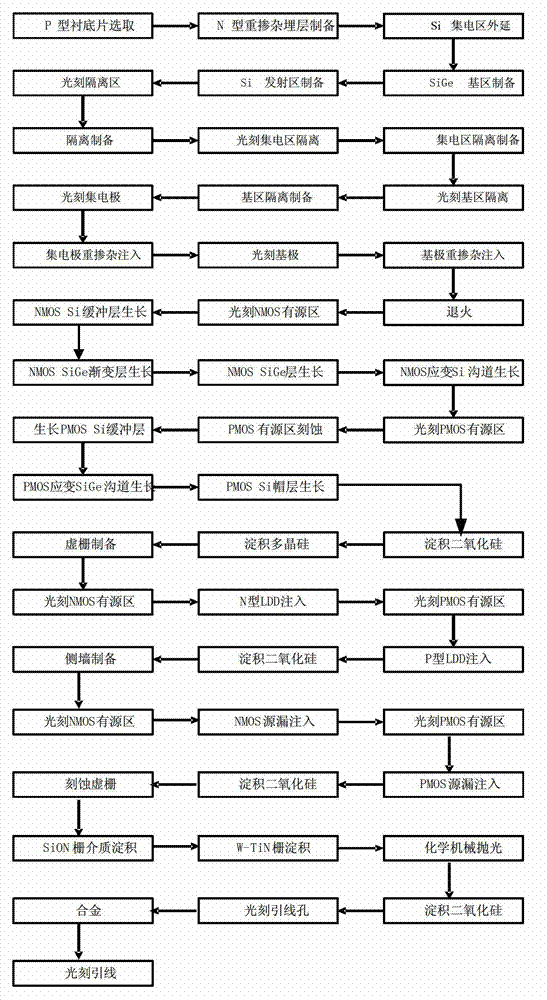

Image

Examples

Embodiment 1

[0117] Embodiment 1: The three-strain BiCMOS integrated device and circuit based on SiGe HBT with a conductive channel of 45nm are prepared, and the specific steps are as follows:

[0118] Step 1, epitaxial growth.

[0119] (1a) Select the doping concentration to be 5×10 14 cm -3 A P-type Si sheet as a substrate;

[0120] (1b) Thermally oxidize a layer of SiO with a thickness of 300nm on the substrate surface 2 layer;

[0121] (1c) Photolithography of the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 800°C for 90 minutes to activate the impurities to form an N-type heavily doped buried layer region;

[0122] (1d) Using chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 2 μm on the upper layer of Si material at 600 ° C, as the collector region, and the doping concentration of this layer is 1× 10 16 cm -3 ;

[0123] (1e) Using chemical vapor deposition (CVD), grow a layer of S...

Embodiment 2

[0183] Embodiment 2: The preparation of a three-strain BiCMOS integrated device and circuit based on SiGe HBT with a conductive channel of 30nm, the specific steps are as follows:

[0184] Step 1, epitaxial growth.

[0185] (1a) Select the doping concentration as 1×10 15 cm -3 A P-type Si sheet as a substrate;

[0186] (1b) Thermally oxidize a layer of SiO with a thickness of 400nm on the substrate surface 2 layer;

[0187] (1c) Photoetching the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 900°C for 60 minutes to activate the impurities to form an N-type heavily doped buried layer region;

[0188] (1d) Using chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 2.5 μm on the upper layer of Si material at 700 ° C, as the collector region, and the doping concentration of this layer is 5 ×10 16 cm -3 ;

[0189] (1e) Using chemical vapor deposition (CVD), grow a layer of SiGe laye...

Embodiment 3

[0249] Embodiment 3: The preparation of a SiGe HBT-based three-strain BiCMOS integrated device and circuit with a 22nm conductive channel, the specific steps are as follows:

[0250] Step 1, epitaxial growth.

[0251] (1a) Select the doping concentration to be 5×10 15 cm -3 A P-type Si sheet as a substrate;

[0252] (1b) Thermally oxidize a layer of SiO with a thickness of 500nm on the surface of the substrate 2 layer;

[0253] (1c) Photolithography of the buried layer region, implanting N-type impurities into the buried layer region, and annealing at 950°C for 30 minutes to activate the impurities to form an N-type heavily doped buried layer region;

[0254] (1d) Using chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 3 μm on the upper layer of Si material at 750 ° C, as the collector region, and the doping concentration of this layer is 1× 10 17 cm -3 ;

[0255] (1e) Using chemical vapor deposition (CVD), grow a layer of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More