Interface conversion module of spaceborne electronic system

An electronic system and interface conversion technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of SpaceWire signal 485 signal and 422 signal can not be converted to each other, poor compatibility, etc., to promote modular design, reduce design costs, promote The effect of resource sharing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

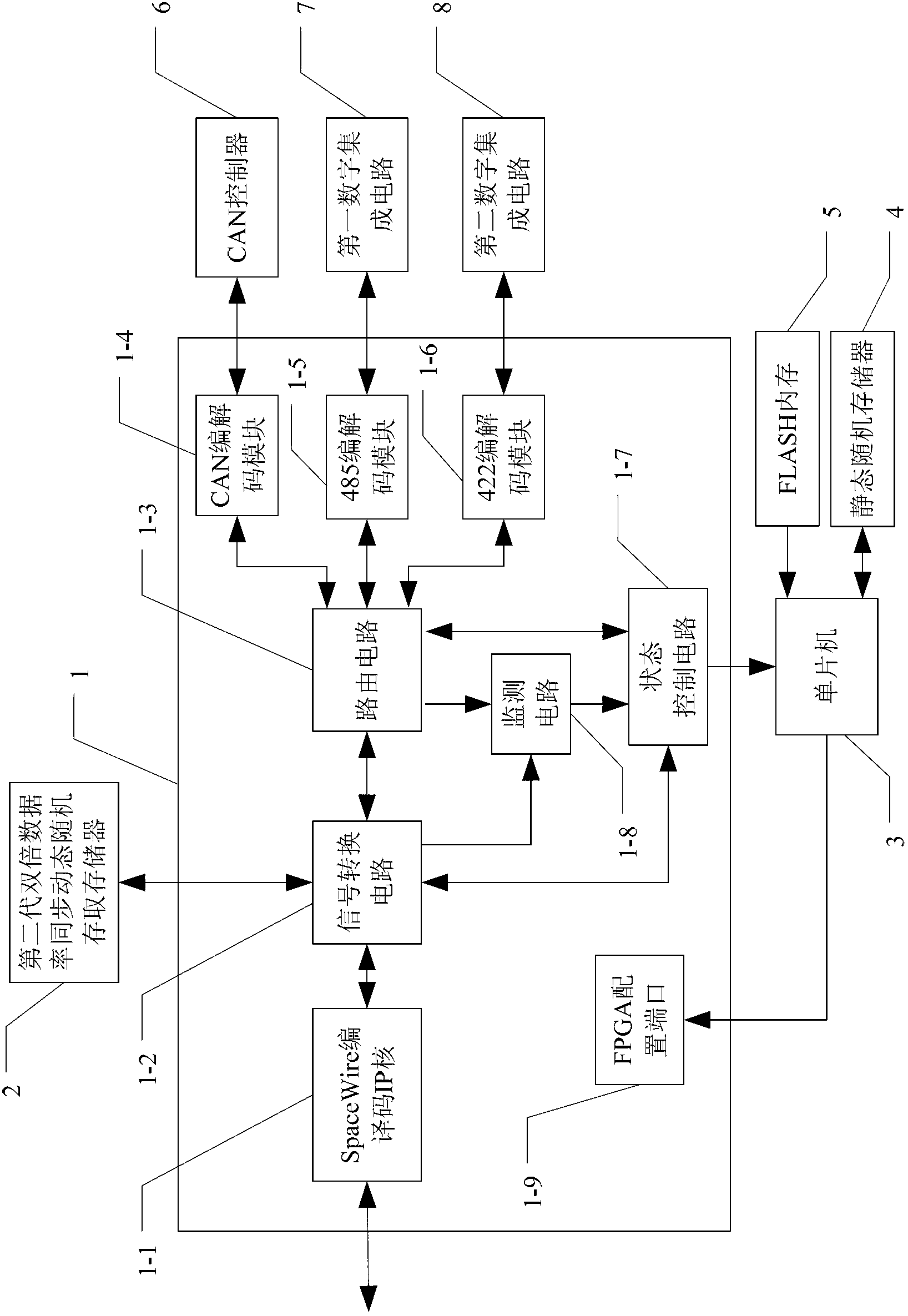

[0028] Specific implementation mode 1. Combination figure 1 Specifically illustrate the present embodiment, the on-board electronic system interface conversion module described in the present embodiment, it comprises the FPGA module 1 based on SRAM, the second generation double data rate synchronous DRAM 2, single-chip microcomputer 3, static Random access memory 4 and FLASH memory 5, described FPGA module 1 based on static random access memory comprises SpaceWire codec IP core 1-1, signal conversion circuit 1-2, routing circuit 1-3, CAN codec module 1-4, 485 codec module 1-5, 422 codec module 1-6, state control circuit 1-7, monitoring circuit 1-8 and FPGA configuration port 1-9,

[0029] The signal conversion circuit 1-2 has a total of: three data signal input and output terminals, one heartbeat signal output terminal and one buffer signal terminal,

[0030] Routing circuits 1-3 have a total of: five data signal input and output terminals and one heartbeat signal output term...

specific Embodiment approach 2

[0050] Specific embodiment two, combine figure 1 Specifically illustrate this embodiment, the difference between this embodiment and the on-board electronic system interface conversion module described in the first embodiment is that it also includes a CAN controller 6, and the data signal input and output terminals of the CAN controller 6 are connected to the The data signal input and output ends of the CAN codec modules 1-4 are connected.

[0051]The CAN data stream in this embodiment is set by the SJA1000 on parameters such as the code rate and clock frequency division, and then input to the on-chip CAN codec module 1-4, decoded to obtain the CAN data frame, and transmit it to the routing circuit 1-3, and the routing circuit 1-3 assigns ports and transmits them to the signal conversion circuit 1-2. The signal conversion circuit 1-2 converts the CAN data frame into a data frame conforming to the SpaceWire protocol, and finally encodes and outputs the IP core 1-1 through Spac...

specific Embodiment approach 3

[0053] Specific embodiment three, combine figure 1 Describe this embodiment in detail. The difference between this embodiment and the on-board electronic system interface conversion module described in the first embodiment is that it also includes a first digital integrated circuit 7, and the data signal of the first digital integrated circuit 7 The input and output ends are connected with the data signal input and output ends of the 485 encoding and decoding modules 1-5.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More