Array substrate, array substrate preparation method and display device

An array substrate and substrate technology, applied in the field of liquid crystal display, can solve the problems of not setting on the grid line area, increasing the pixel aperture ratio, image flickering, etc., and achieve the goal of increasing the aperture ratio, reducing energy consumption, and saving costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

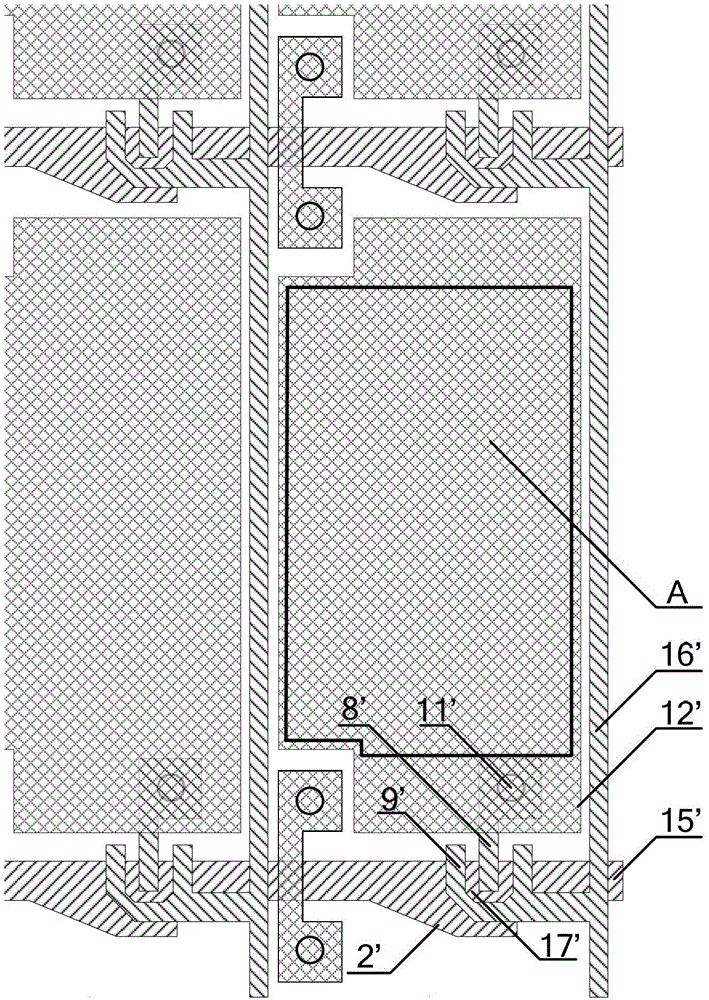

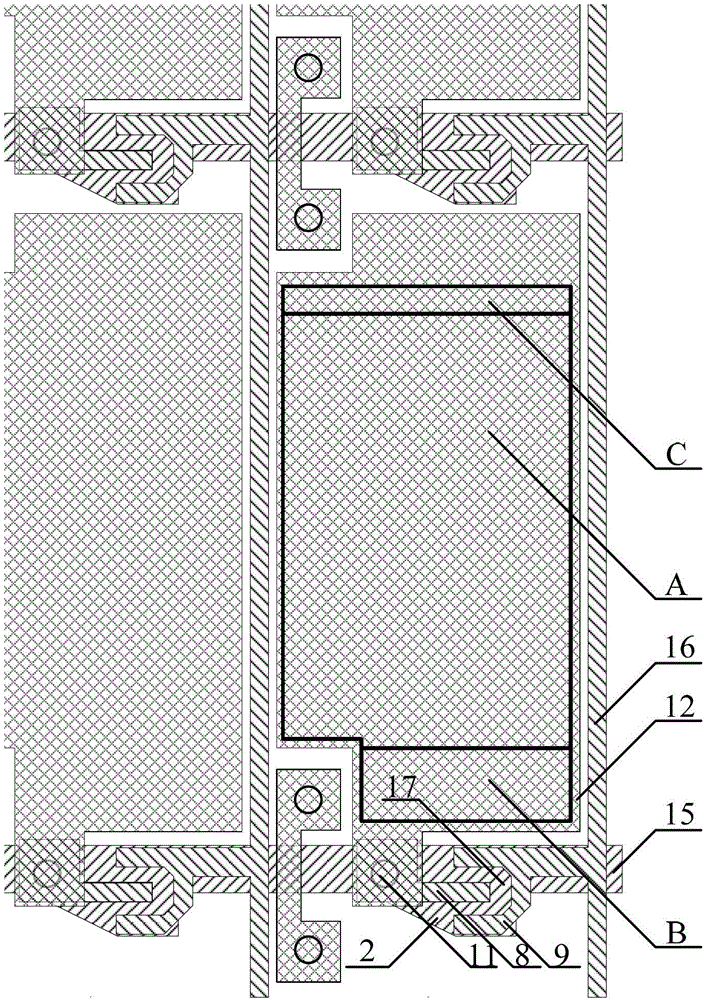

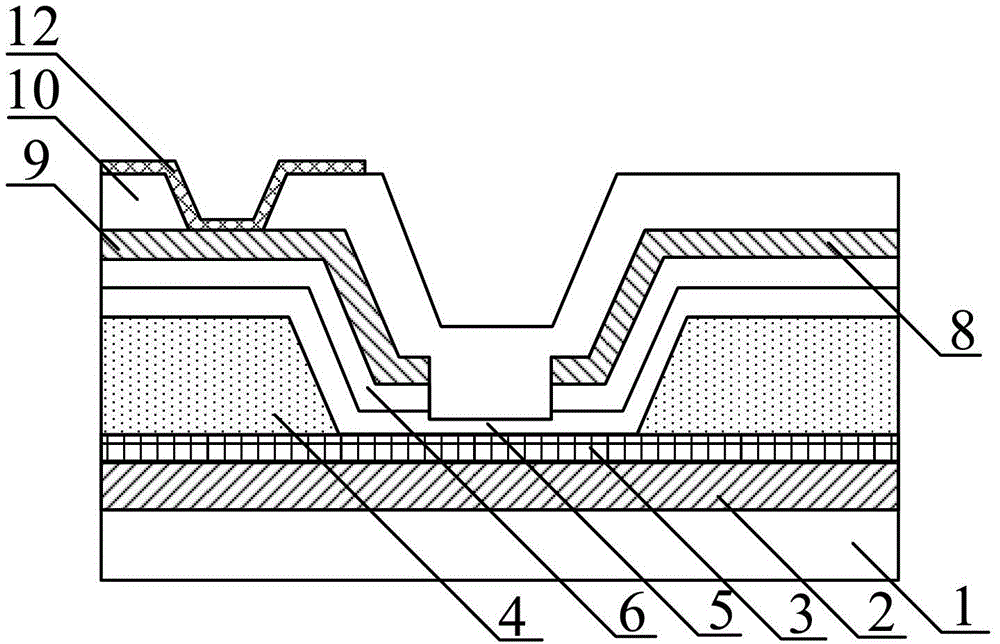

[0070] like figure 2 An array substrate shown in the figure, the structure of a pixel unit is shown in the figure; image 3 Yes figure 2 A cross-sectional view of the mid-array substrate; it includes data lines 16 and gate lines 15 formed on the substrate 1, the data lines 16 and the gate lines 15 define a pixel area, and a thin film transistor and a pixel electrode 12 are formed in the pixel area, and the gate lines 15 is used to provide a turn-on signal to the thin film transistor, and the data line 16 is used to provide a data signal to the pixel electrode 12; the thin film transistor includes: a gate electrode 2 formed on the substrate 1 and connected to the gate line 15; formed on the gate line 15 and the gate The gate insulating layer 3 on the electrode 2 and covering the entire substrate; the active layer formed on the gate insulating layer 3, the drain electrode 8 formed above the active layer and the source electrode opposite to the drain electrode 8 and connected ...

Embodiment 2

[0076] The present invention also provides a method for preparing the above-mentioned array substrate, which mainly includes forming gate lines and gate electrodes on the substrate, and forming a gate insulating layer covering the entire substrate on the gate lines and gate electrodes; Drain electrode and source electrode; a filling layer is formed between the gate electrode and the drain electrode and the source electrode; a passivation layer is formed on the source electrode, the drain electrode and the channel region; the position where the passivation layer is located above the gate line and the drain electrode Opening a passivation layer via hole; forming a pixel electrode connected to the drain electrode through the passivation layer via hole. In this embodiment, a filling layer is formed between the gate electrode, the drain electrode and the source electrode as an example for description.

[0077] Flow chart such as Figure 4 The shown method for preparing an array su...

Embodiment 3

[0101] The present invention also provides a display device including any one of the above array substrates.

[0102] The present invention also provides a display device, including the array substrate described in the first embodiment; because the pixel aperture ratio is increased, the display device has light transmittance and resolution, and because the energy consumption of the backlight module is reduced , saving costs and improving display quality.

[0103] The above-mentioned display device may be a display panel, electronic paper, OLED (Organic Light Emitting Diode, organic light-emitting diode) panel, liquid crystal TV, liquid crystal display, digital photo frame, mobile phone, tablet computer and other products or components with any display function.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More