A power ldmos device with junction field plate

A junction field plate and device technology, applied in semiconductor devices, electrical components, diodes, etc., can solve the problems of reducing on-resistance, affecting the breakdown characteristics of devices, occupying the area of current flow, etc., to reduce on-resistance, Improved breakdown characteristics and reduced reverse current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

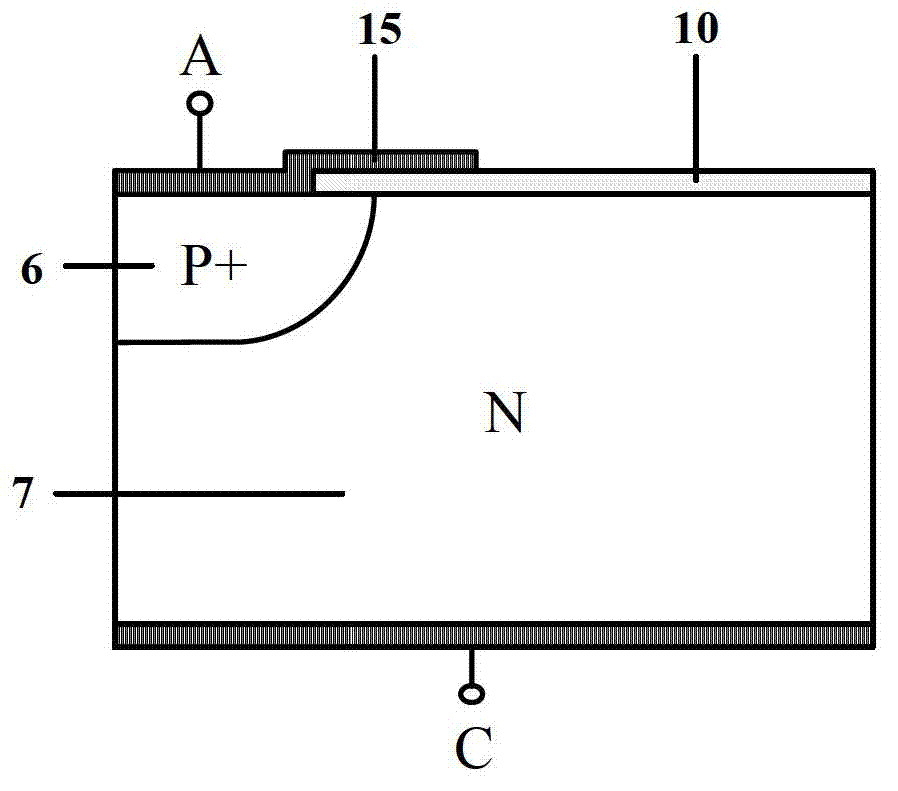

[0039] Figure 6 It is a schematic diagram of the structure of a power LDMOS device with JFP proposed by the present invention, including a substrate 1, an N buried layer 2, a P-type body region 4, a source region 5, a body contact region 6, an active layer 7, a drain region 8, and electrode isolation Dielectric layer 9, gate dielectric 10a, gate electrode conductive material 10b, P-type ohmic contact region 11, P-type high resistance region 12, N-type ohmic contact region 13, field dielectric 14, source electrode S, gate electrode G, and drain electrode D , where the active layer between the body region 4 and the drain region 8 is called the drift region.

[0040] The P-type ohmic contact region 11, the P-type high resistance region 12, the N-type ohmic contact region 13 and the field medium 14 form a junction field plate structure JFP located on the surface of the device; wherein the P-type ohmic contact region 11 is electrically connected to the source electrode S, The N-t...

Embodiment approach 2

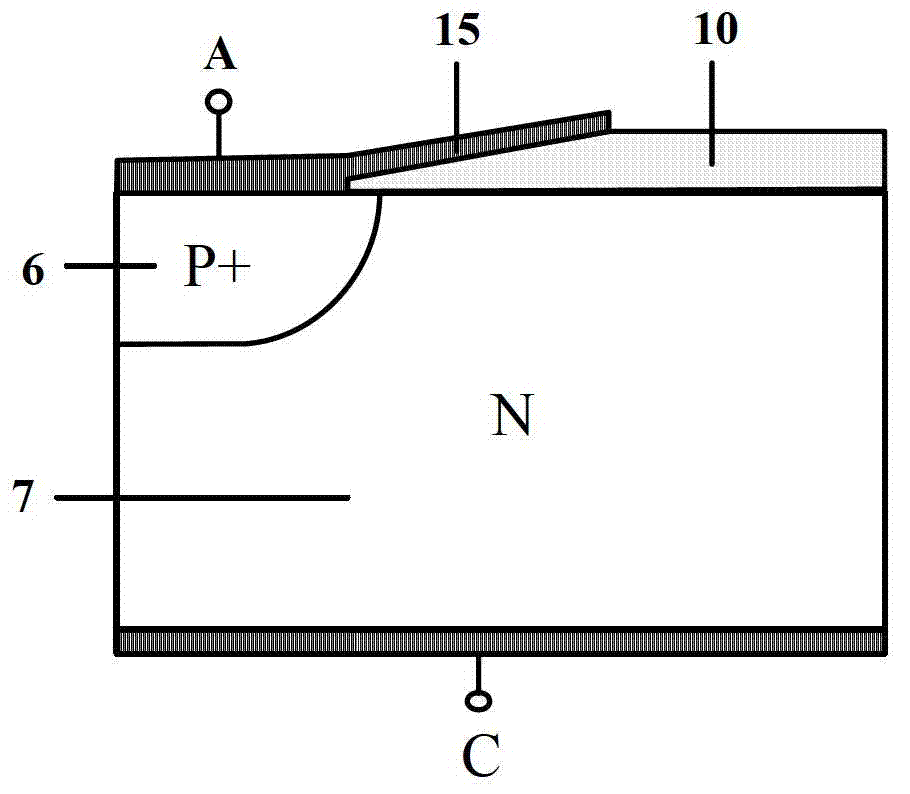

[0044] Figure 7 It is a schematic structural diagram of a JFP high-voltage LDMOS device with an N-type buffer zone 12c in a junction field plate proposed by the present invention; and Figure 6 Compared with the structure shown, an N-type buffer area 12c is added between the P-type high resistance region 12 and the N-type ohmic contact region 13, and the doping concentration of the N-type buffer region 12c is lower than that of the N-type ohmic contact region 13 . The added N-type buffer zone 12c can alleviate the electric field peak of the device between the N-type ohmic contact region 13 and the P-type semiconductor layer 12d, which is beneficial to improve the withstand voltage characteristics of the device.

Embodiment approach 3

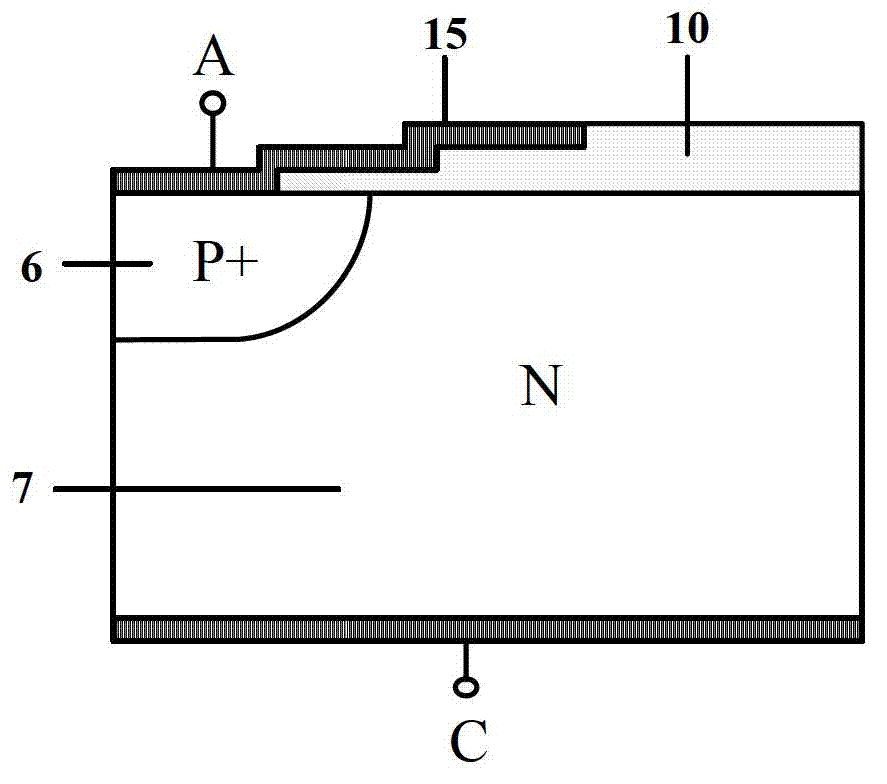

[0046] Figure 8 It is a schematic structural diagram of a JFP power LDMOS device provided by the present invention with a part of the buried layer 2 of the semiconductor of the second conductivity type. and Figure 6 Compared to the shown structure, Figure 8 The middle part of the N-type buried layer 2 is in the substrate 1 below the drain terminal. At this time, the N-type buried layer 2 can also improve the vertical withstand voltage of the device; at the same time, compared with the case of the entire N-type buried layer 2, the partial N-type buried layer 2 It is beneficial to reduce the substrate leakage current.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More