Method for preparing gate silicon oxide layers and method for processing semiconductor substrate

A technology of gate silicon oxide and processing method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of affecting channel carrier mobility, complicated process, and reducing carrier mobility, etc. Achieve the effects of surface property optimization, process simplification, and reliability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

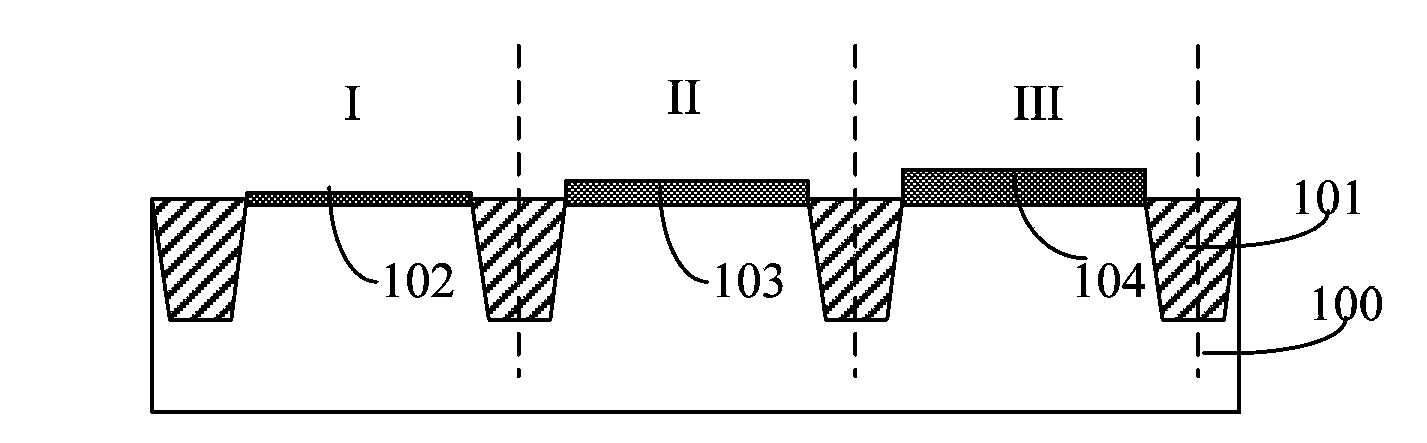

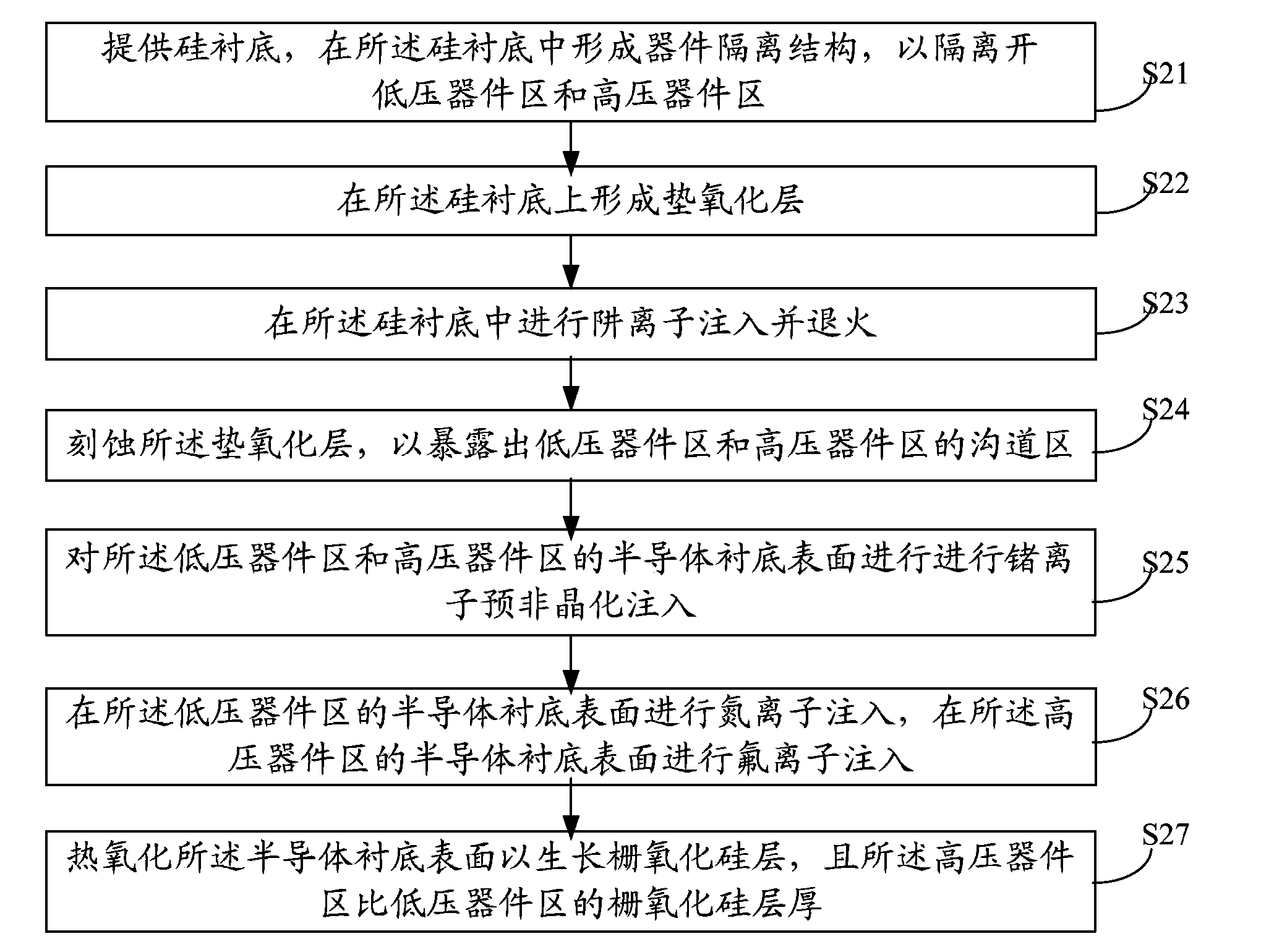

[0042] Such as figure 2 As shown, this implementation provides a method for preparing a gate silicon oxide layer, comprising the following steps:

[0043] S21, providing a silicon substrate, forming a device isolation structure in the silicon substrate to isolate the low-voltage device region and the high-voltage device region;

[0044] S22, forming a pad oxide layer on the silicon substrate;

[0045] S23, performing well ion implantation and annealing in the silicon substrate;

[0046] S24, etching the pad oxide layer to expose the channel region of the low-voltage device region and the high-voltage device region;

[0047] S25, performing pre-amorphization implantation of germanium ions on the surface of the semiconductor substrate in the low-voltage device region and the high-voltage device region;

[0048] S26, performing nitrogen ion implantation on the surface of the semiconductor substrate in the low-voltage device region, and performing fluorine ion implantation on ...

Embodiment 2

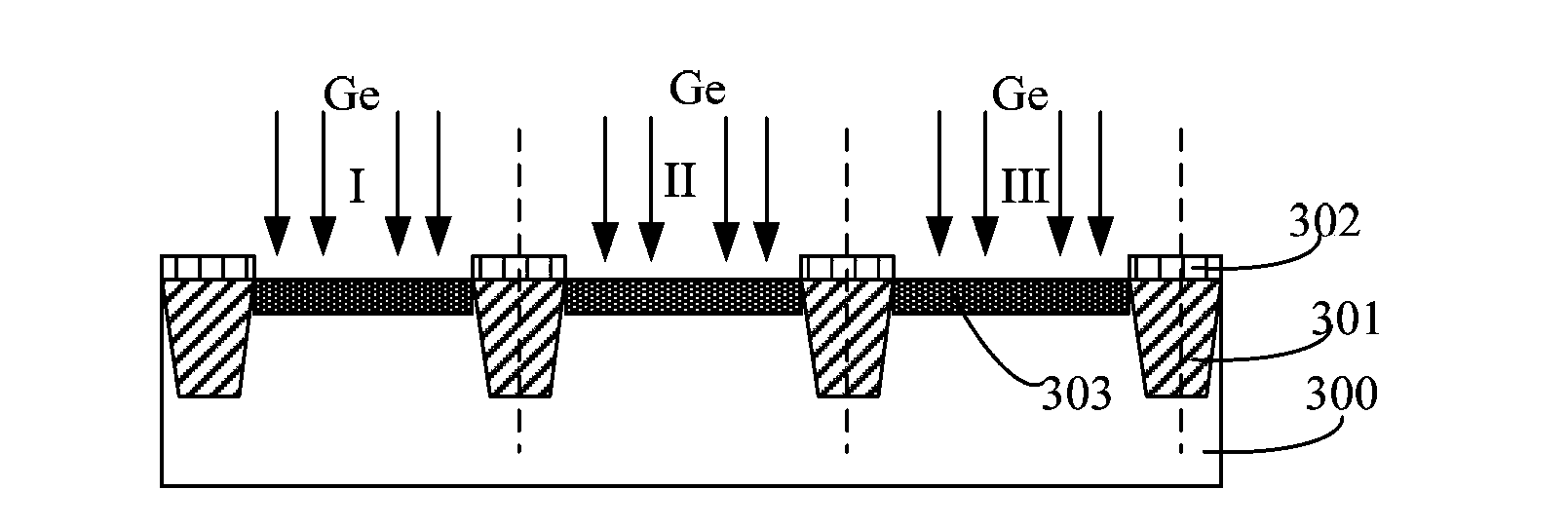

[0065] Such as Figure 4 As shown, this implementation provides a method for preparing a gate silicon oxide layer, comprising the following steps:

[0066] S41, providing a silicon substrate, forming a device isolation structure in the silicon substrate to isolate a low-voltage device region and a high-voltage device region;

[0067] S42, forming a pad oxide layer on the silicon substrate;

[0068] S43, performing well ion implantation and annealing in the silicon substrate;

[0069] S44, performing pre-amorphization implantation of germanium ions on the surface of the semiconductor substrate in the low-voltage device region and the high-voltage device region;

[0070] S45, performing nitrogen ion implantation on the surface of the semiconductor substrate in the low-voltage device region, and performing fluorine ion implantation on the surface of the semiconductor substrate in the high-voltage device region;

[0071] S46, etching the pad oxide layer to expose the channel re...

Embodiment 3

[0087] Such as Figure 7 As shown, the present embodiment provides a method for processing a semiconductor substrate, comprising the following steps:

[0088] S71, providing a semiconductor substrate, where the semiconductor substrate includes a plurality of subregions;

[0089] S72, perform nitrogen ion implantation on the surface of one subregion of the semiconductor substrate, and perform fluorine ion implantation on the surface of another subregion of the semiconductor substrate;

[0090] S73. Thermally oxidize the surface of the semiconductor substrate to grow an oxide layer, and the oxide layer in the sub-region implanted with fluorine ions is thicker than the sub-region implanted with nitrogen ions.

[0091] The semiconductor substrate provided in step S71 includes a plurality of sub-regions, and these sub-regions may be the high-voltage device region and the low-voltage device region described in Embodiment 1 and Embodiment 2, or may be device isolation trenches.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More