Method for improving gap filling capability

A technology for filling capacity and voids, which is applied in the field of semiconductor device manufacturing, can solve problems such as reduced filling capacity, affecting CONT filling, and shorting of CONT, and achieves the effect of reducing aspect ratio and enhancing void filling capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

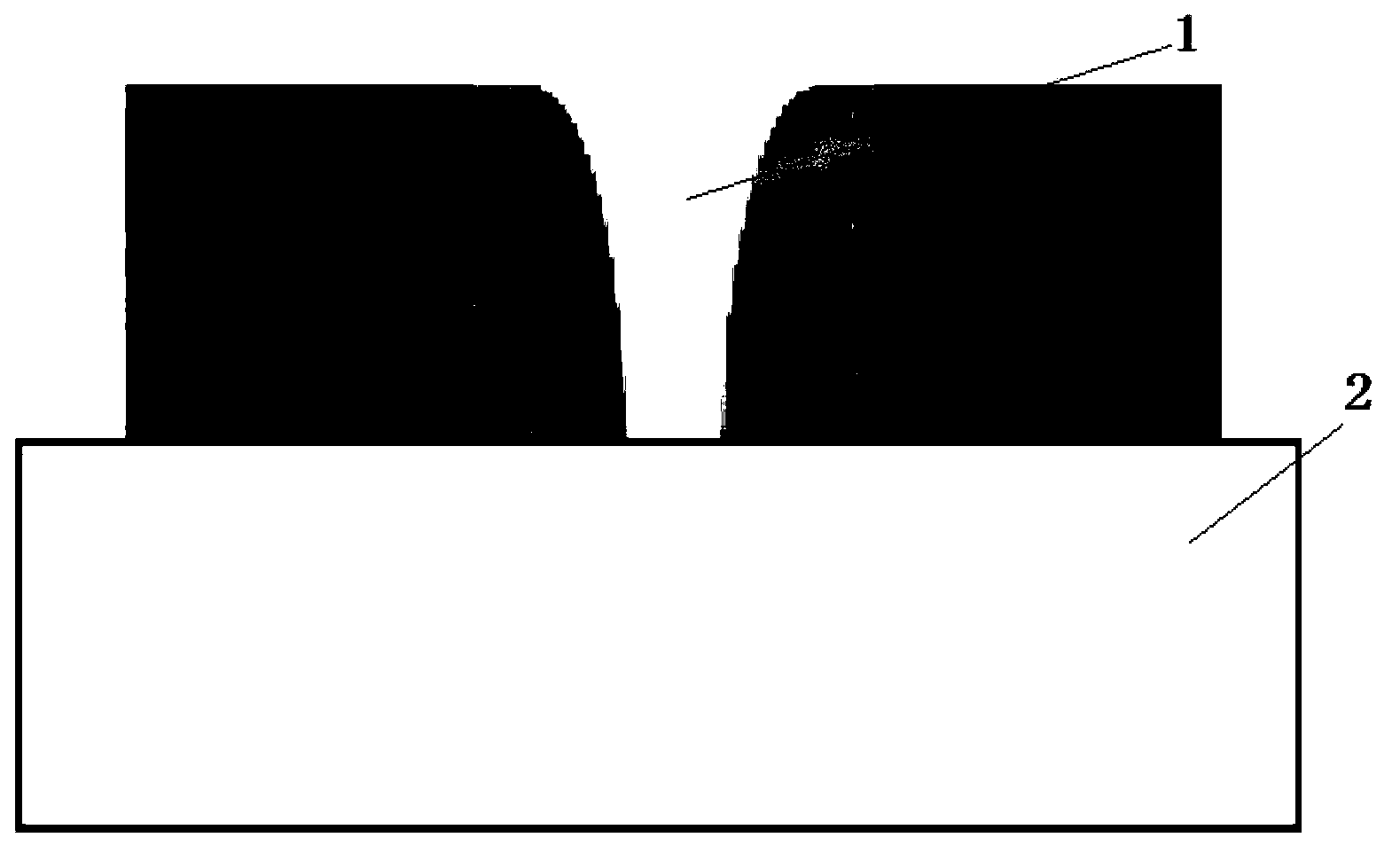

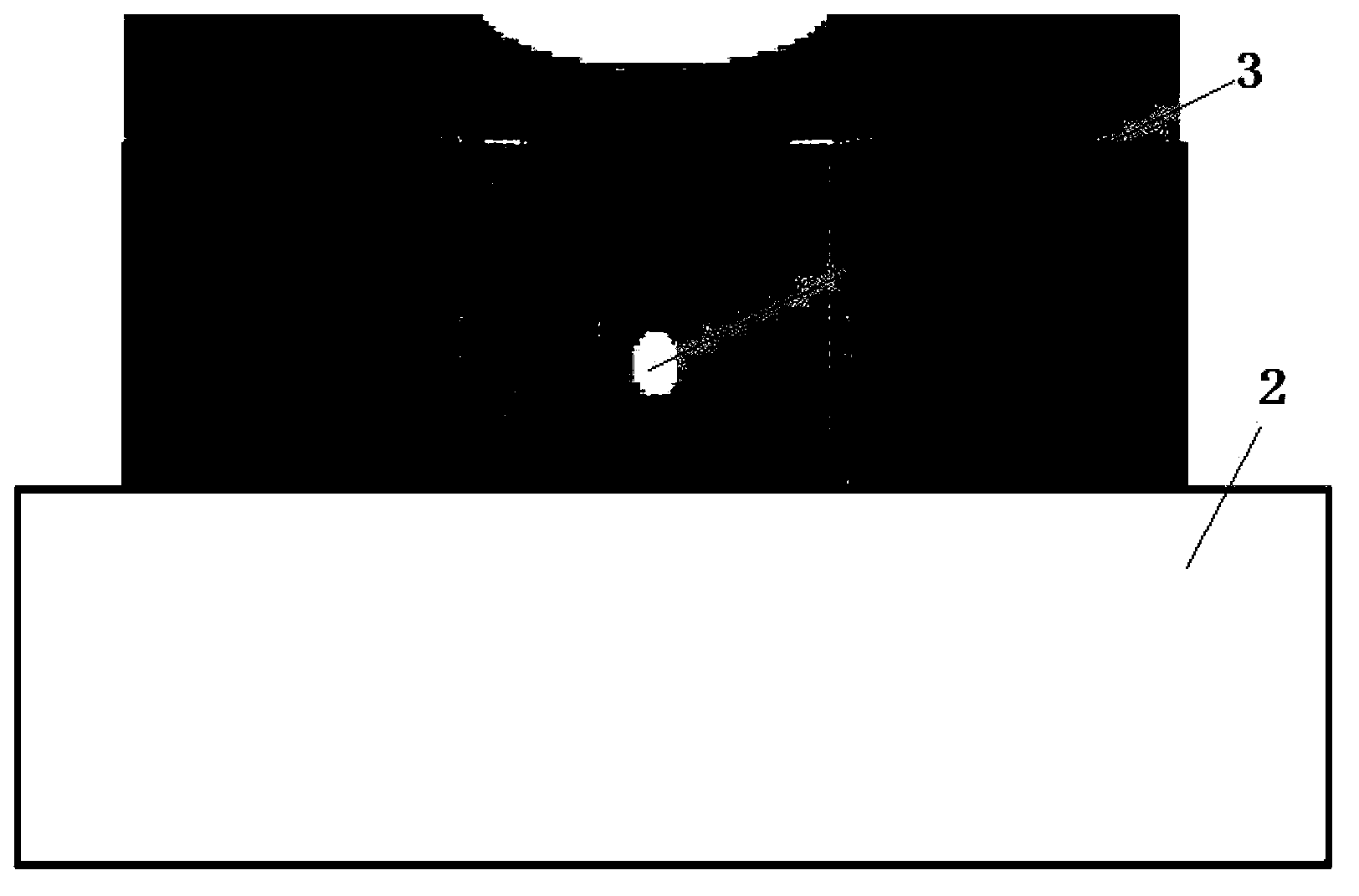

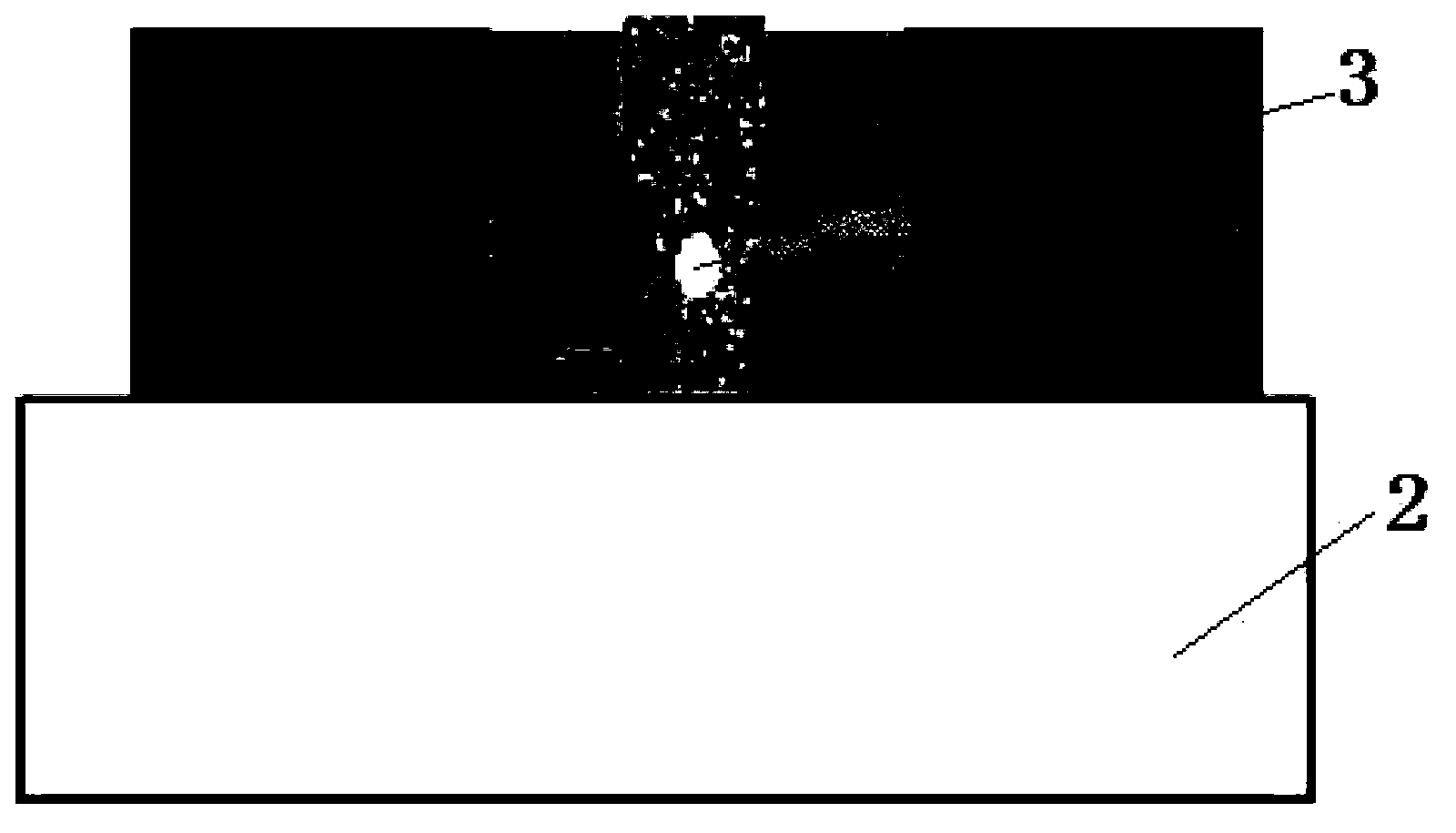

[0036] As shown in Figures 1 and 2, a method for improving the gap filling capability includes the following steps: Step 1: Forming a spacer 1 with a certain aspect ratio on the ONO structure by etching; Step 2: Using DHF to form a spacer 1 1. Carry out secondary etching, DHF etching residence time is determined according to the needs of different methods, and reduce the aspect ratio of the spacer; Step 3: Fill the spacer with ILD; Step 4: Carry out metal tungsten film growth. Among them, the ONO structure is a silicon oxide-silicon nitride-silicon oxide layer, and the formation method is chemical vapor deposition (VCD).

[0037] In this embodiment, compared with the traditional method, an acid tank etching process is added. Since DHF has a high ET (residence time) selectivity ratio for the oxide layer, after DHF acid tank etching, the width of the upper part of the spacer is enlarged. , thereby enlarging the filling window of the ILD, reducing the aspect ratio of the spacer, ...

Embodiment 2

[0039] A method for manufacturing a chip, comprising the steps of: step 1. making a crystal garden, and the chip as a substrate 2; step 2. generating an oxide layer on the substrate made in step 1, coating the oxide layer with photoresist, exposing, Developing and baking; Step 3. Perform acid etching to form a spacer with a certain aspect ratio; Step 4. Use DHF to perform secondary etching to reduce the aspect ratio in Step 3; Step 5. Clean and dry; Step 6 . Perform plasma bath and metal etching, remove photoresist, make metal film, and make pathways in the chip; Step 7. Perform ion implantation, and change the electrical characteristics of some areas as required; Step 8. Post-package the chip.

[0040] The chip made by adopting this embodiment can effectively avoid the generation of pores 3 during the filling process due to the improved gap filling ability of the spacer, and avoid subsequent filling materials from diffusing from the pores, thereby avoiding the occurrence of pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More