Circuit for solving inconsistency of gains among batches of chips

A batch-to-batch, consistent technology, applied in gain control, electrical components, amplification control, etc., can solve problems such as unfavorable system integration, complex circuit structure, increase system power consumption, etc. Strong operability without affecting system noise and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

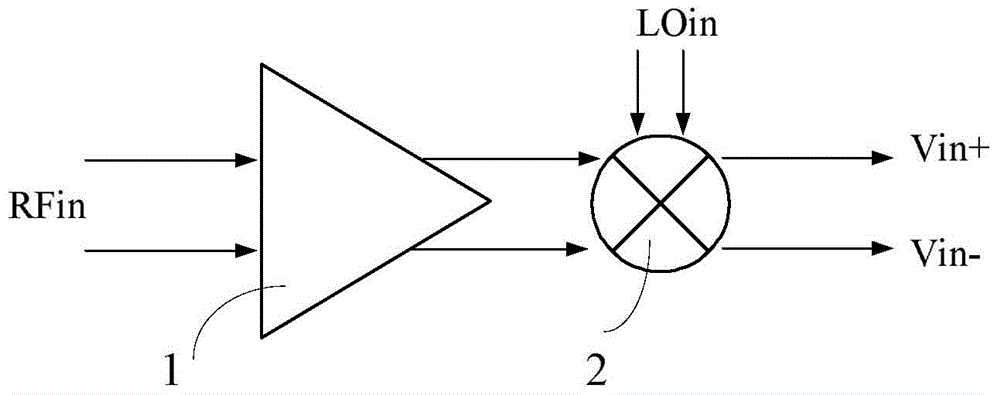

[0023] see figure 1 , The CMOS RF receiving front-end chip includes a low noise amplifier 1 and a mixer 2 . After the differential radio frequency signal RFin is amplified by the low noise amplifier 1 , it is mixed with the local oscillator signal LOin by the mixer 2 to output a positive output signal Vin+ and a negative output signal Vin−.

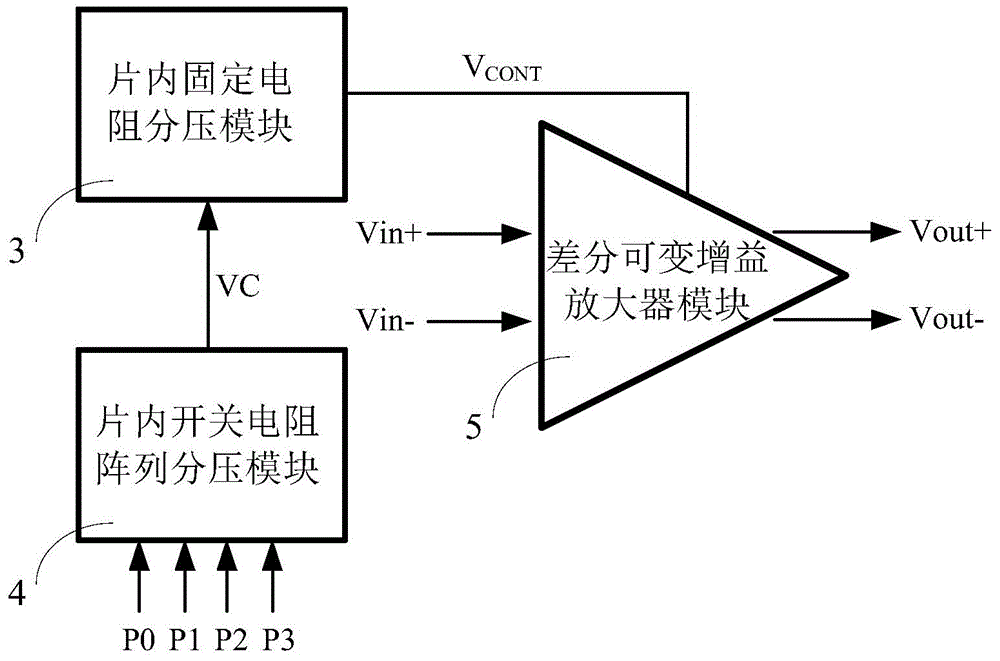

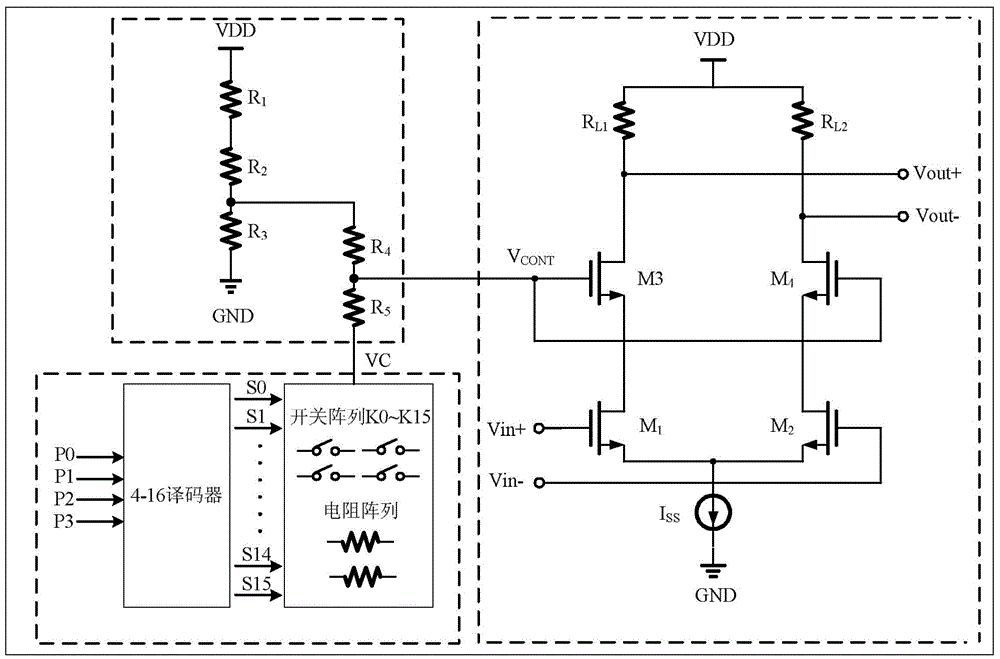

[0024] The circuit of the present invention is used to solve figure 1 The problem of inconsistency in gain between batches of CMOS RF receiving front-end chips. Please combine figure 2 , the circuit includes an on-chip fixed resistor voltage divider modul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More