Isolation structure and formation method thereof

A technology of isolation structure and trench, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of low deposition efficiency, high cost, and insufficient oxide quality, so as to improve the isolation effect, reduce the difficulty, The effect of improving fill quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

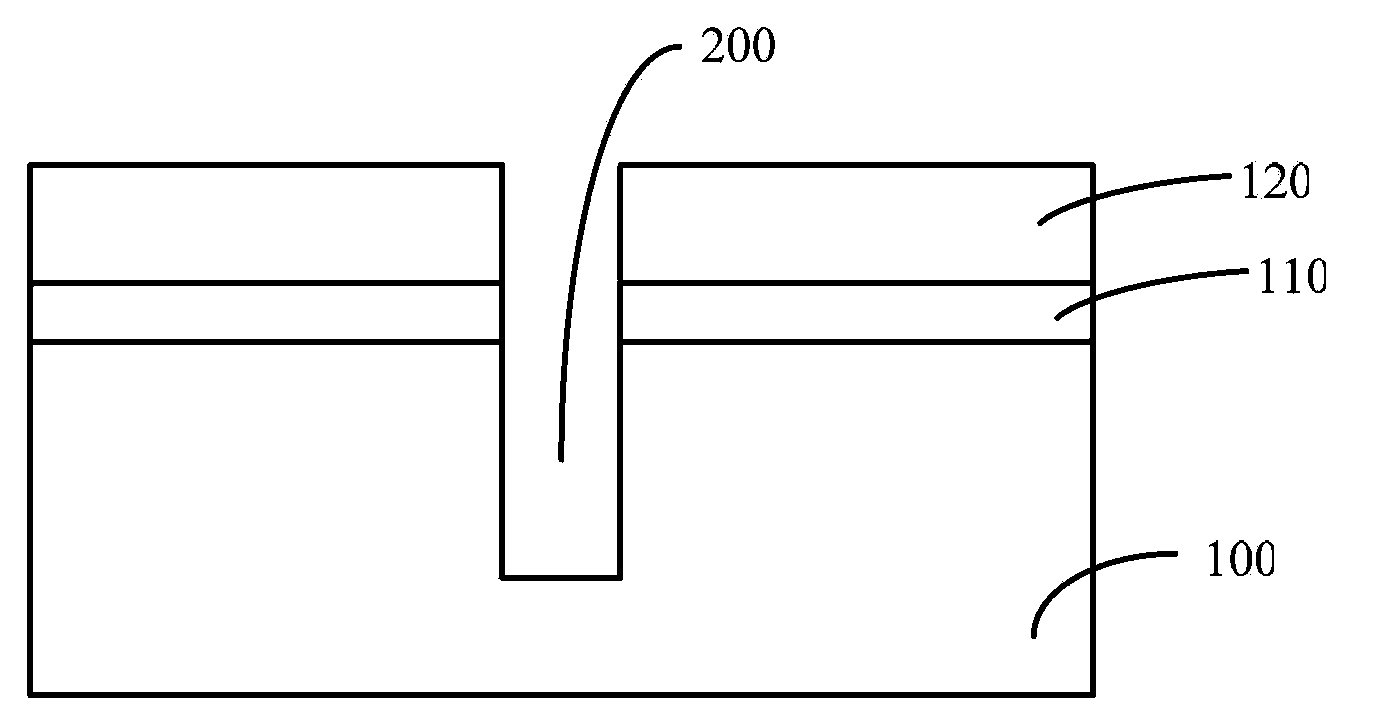

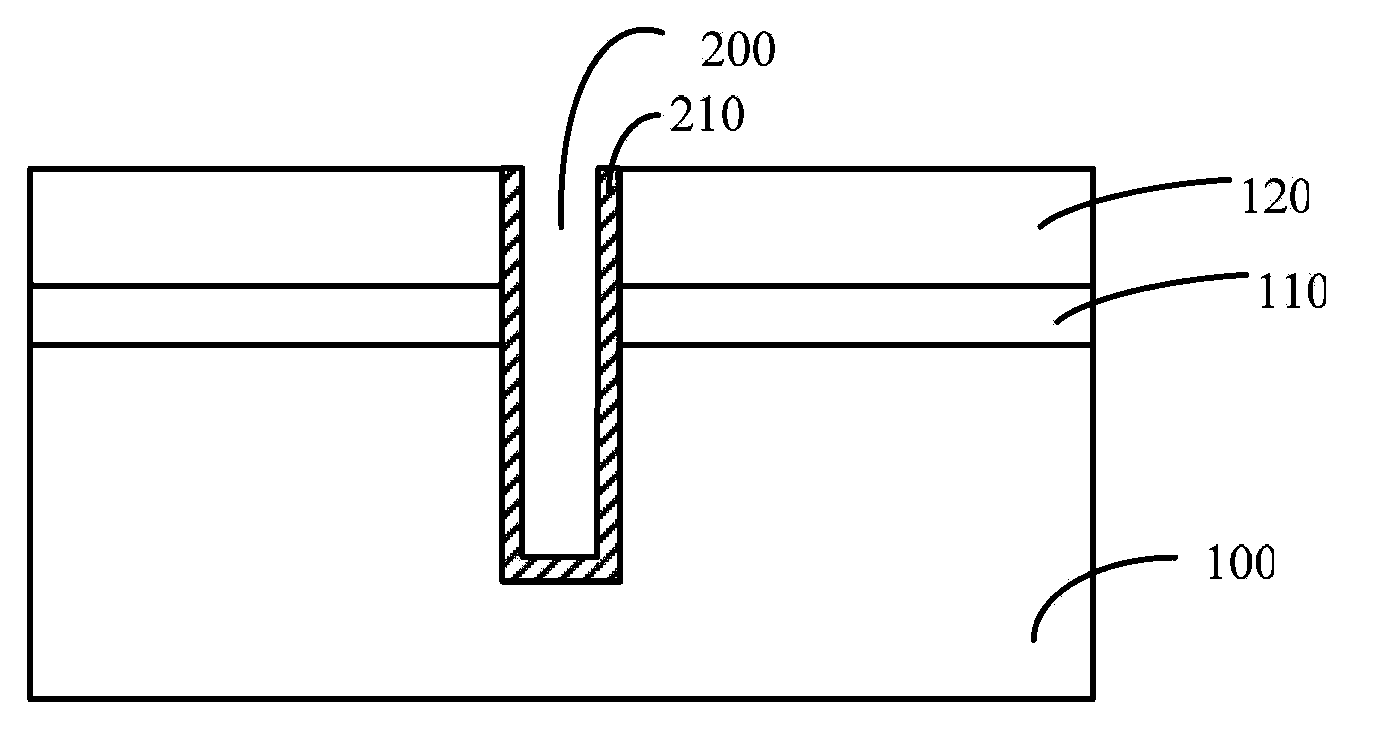

[0035] Please refer to figure 1 A semiconductor substrate 100 is provided, the surface of the semiconductor substrate has a mask layer, and the mask layer includes a silicon oxide layer 110 on the surface of the substrate and a silicon nitride layer 120 on the surface of the silicon oxide layer 110 . Trenches 200 are formed in the semiconductor substrate.

[0036] Specifically, the material of the semiconductor substrate 100 includes semiconductor materials such as silicon, germanium, silicon germanium, and gallium arsenide, and may be a bulk material or a composite structure such as silicon-on-insulator. Those skilled in the art can select the type of the semiconductor substrate 100 according to the semiconductor devices formed on the semiconductor substrate 100 , so the type of the semiconductor substrate should not limit the protection scope of the present invention. In this embodiment, bulk silicon is used as the semiconductor substrate.

[0037]The silicon oxide layer ...

no. 2 example

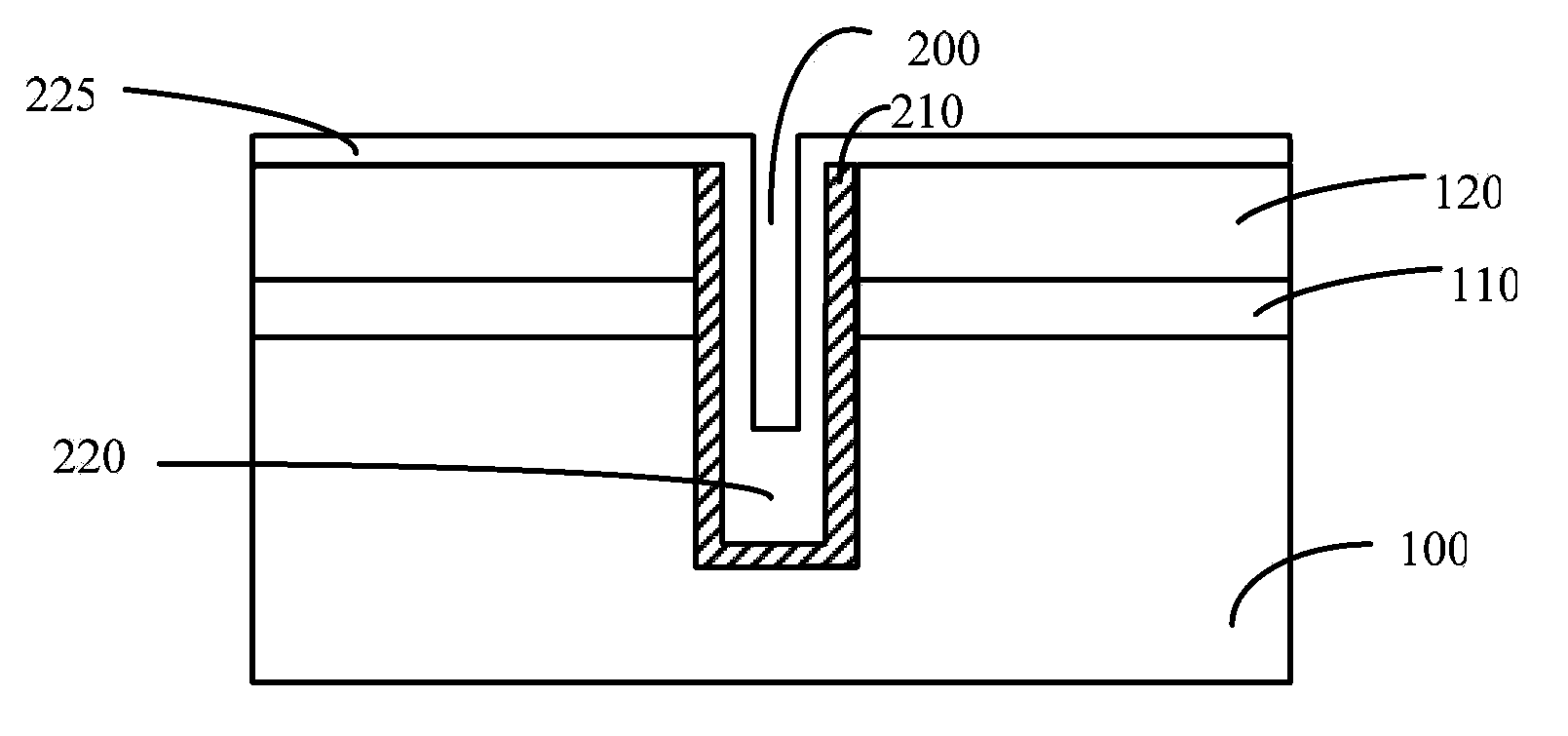

[0059] Please refer to Image 6 , in the second embodiment of the present invention, after forming the second dielectric material in the trench according to the method in the first embodiment, before forming the third dielectric material layer, the sidewalls covering the unfilled upper part of the trench are removed, The side walls of the hard mask layer on both sides of the opening above the groove, and the second dielectric film on the surface of the hard mask layer.

[0060] The process of removing the second dielectric film 225 is wet etching, and the etching solution is HF. The first dielectric layer 210 and the silicon nitride layer 120 are used as an etching stop layer. Specifically, the second dielectric material is annealed first, and after the second dielectric layer 220 and the second dielectric film 225 are formed, the second dielectric film 225 is removed.

[0061]In other embodiments of the present invention, before annealing the second dielectric material, a w...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More