Chip-level atomic clock air chamber and manufacturing method thereof

A chip-level atomic clock and gas chamber technology, applied to instruments using atomic clocks, can solve the problems of unfavorable atomic clock stability, large gas chamber volume, and increased complexity, and achieve simple and reasonable gas chamber structure, small volume, and simple use Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] Embodiment 1: A chip-scale atomic clock gas chamber

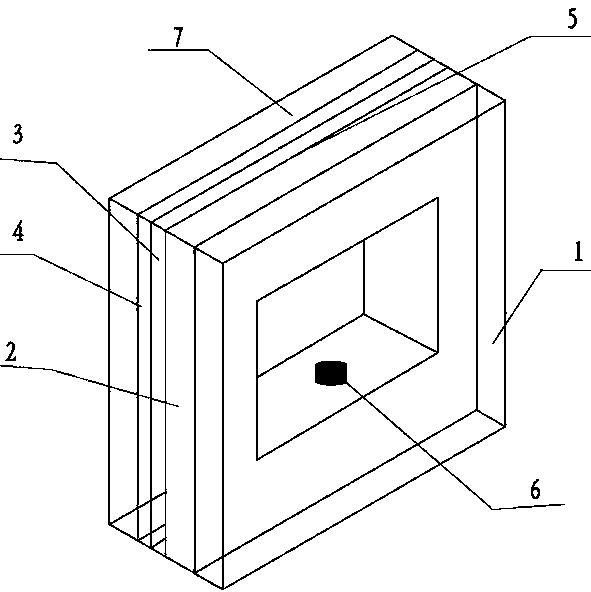

[0028] attached figure 1 The schematic diagram of the structure of the chip-scale atomic clock gas chamber provided for this embodiment; see the attached figure 1 , the chip-level atomic clock gas chamber includes glass 1, SOI silicon wafer 5, alkali metal rubidium 6 and support layer 7, which is a support layer-SOI silicon wafer-glass structure, and the substrate layer 2 of the SOI silicon wafer 5 has a cavity as a cavity Groove, alkali metal rubidium 6 is placed in the groove and filled with inert gas; the substrate layer 2 of the SOI silicon wafer is connected to the glass 1 through electrostatic bonding; the device layer 4 side of the SOI silicon wafer is spin-coated with epoxy resin as a support Layer 7.

[0029] The specific preparation method is as follows:

[0030] (1) RCA standard cleaning steps are used to clean SOI silicon wafers; thermally oxidize and grow oxide layers on both sides of the cleaned sili...

Embodiment 2

[0034] Example 2: Preparation of a chip-scale atomic clock gas chamber

[0035] (1) RCA standard cleaning steps are used to clean SOI silicon wafers; thermally oxidize and grow oxide layers on both sides of the cleaned silicon wafers, and deposit silicon nitride on the oxide layers by LPCVD; The bottom side is photolithographically etched, silicon nitride and silicon oxide are etched to expose part of the silicon wafer, and the silicon wafer without silicon nitride and silicon oxide protection is removed by single-sided KOH wet etching, until the buried layer of the SOI silicon wafer is removed. Thereby preparing a groove as a cavity;

[0036] (2) In the glove box, in a nitrogen atmosphere, place the alkali metal cesium in the groove;

[0037] (3) In the bonding equipment, in an argon atmosphere, conduct silicon-glass electrostatic bonding on the side of the SOI silicon wafer with the substrate through electrostatic bonding, and the cavity has been sealed so far;

[0038] (4...

Embodiment 3

[0039] Example 3: Preparation of a chip-scale atomic clock gas chamber

[0040](1) RCA standard cleaning steps are used to clean SOI silicon wafers; thermally oxidize and grow oxide layers on both sides of the cleaned silicon wafers, and deposit silicon nitride on the oxide layers by LPCVD; The bottom side is photolithographically etched, silicon nitride and silicon oxide are etched to expose part of the silicon wafer, and the silicon wafer without silicon nitride and silicon oxide protection is removed by single-sided KOH wet etching, until the buried layer of the SOI silicon wafer is removed. Thereby preparing a groove as a cavity;

[0041] (2) In the glove box, in a nitrogen atmosphere, place cesium chloride and barium nitride in the groove;

[0042] (3) In the bonding equipment, in the argon / nitrogen mixed gas with a volume ratio of 1:1.4, the silicon-glass electrostatic bonding is carried out on the side of the above-mentioned SOI silicon wafer with the substrate by elec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More