Micro-fluidic chip and micro-fluidic chip system for single cell analysis and single cell analyzing method

A microfluidic chip and single-cell technology, applied in the field of single-cell analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

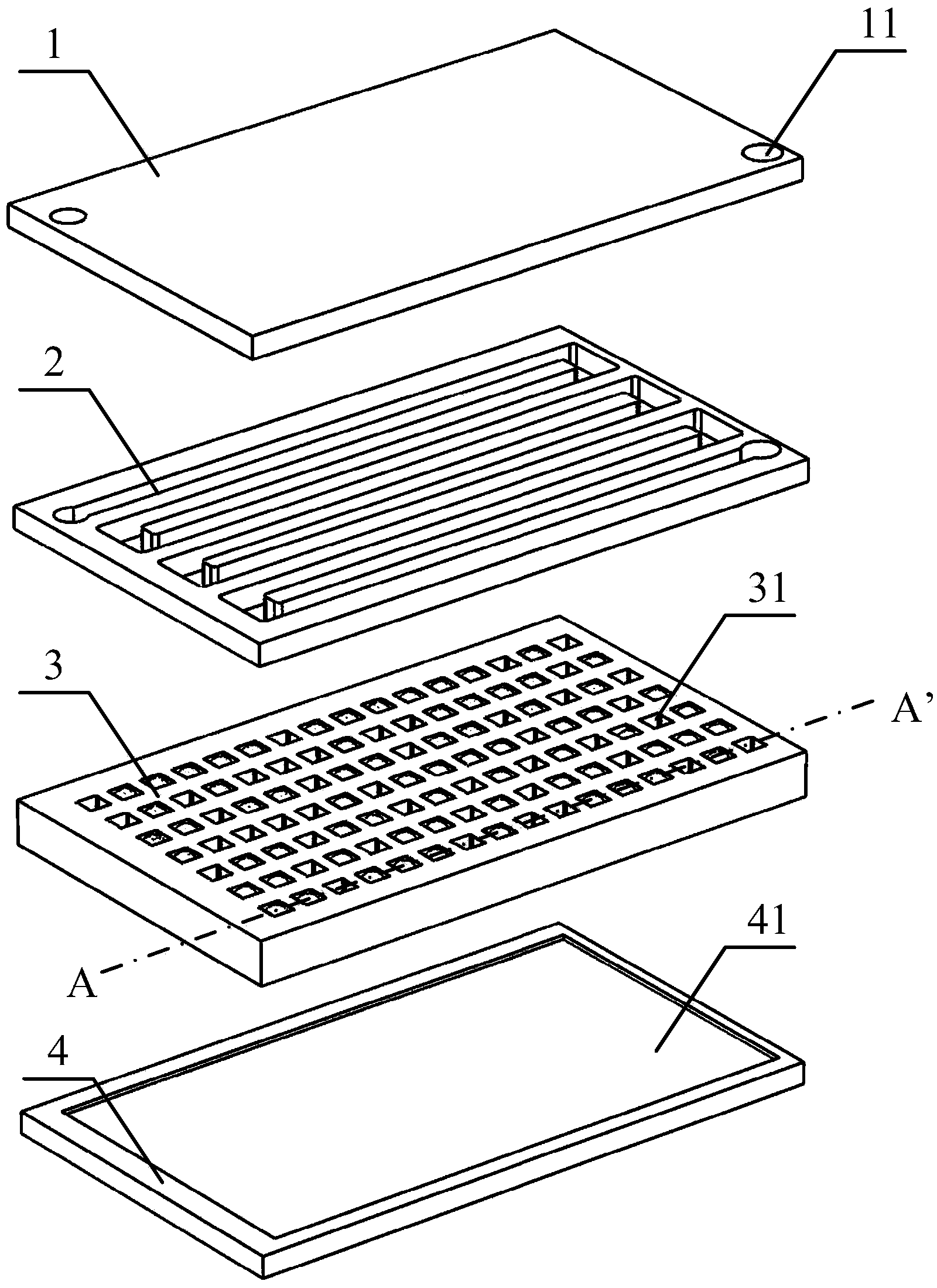

Embodiment 1

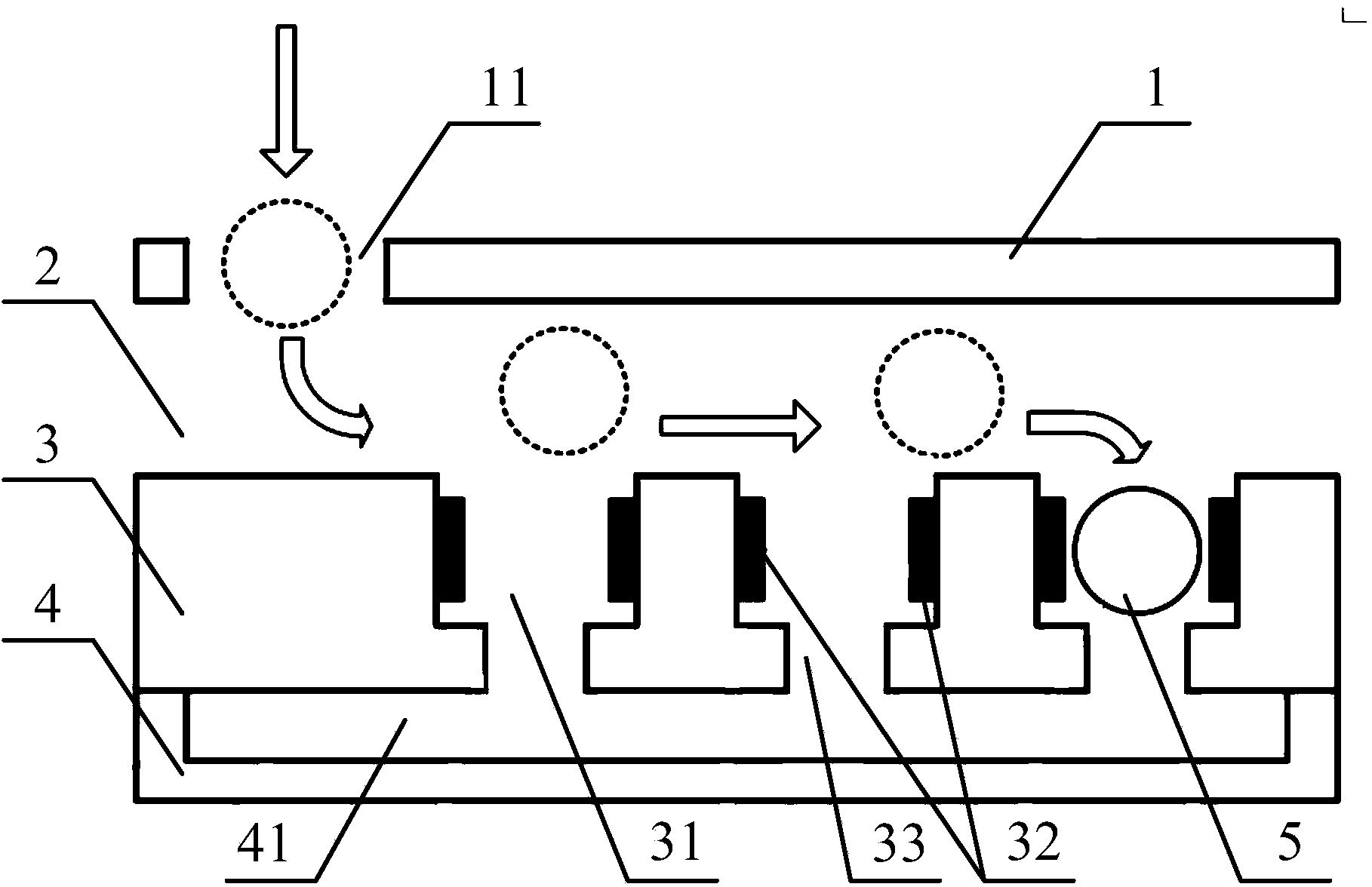

[0072] Transparent top cover: Use 4-inch Pyrex7740 glass sheet (Corning Corporation), cut into rectangular small pieces according to the external dimensions of 2 cm long and 1 cm wide, and punch two holes in specific positions of each small piece with a laser.

[0073] Microfluidic channel: N-type 4-inch silicon wafer is used. After the planar shape of the microfluidic channel is photoetched, ICP dry etching (inductive plasma etching, which uses sulfur hexafluoride and tetrafluoride High-energy plasma of carbon to etch silicon) to create trenches 30 microns deep. Pour the liquid PDMS into the tank, remove it from the mold after it solidifies, cut off the part of the PDMS without the tank, and cut it into rectangular pieces according to the dimensions of 2 cm long and 1 cm wide, thus obtaining microfluidic channels.

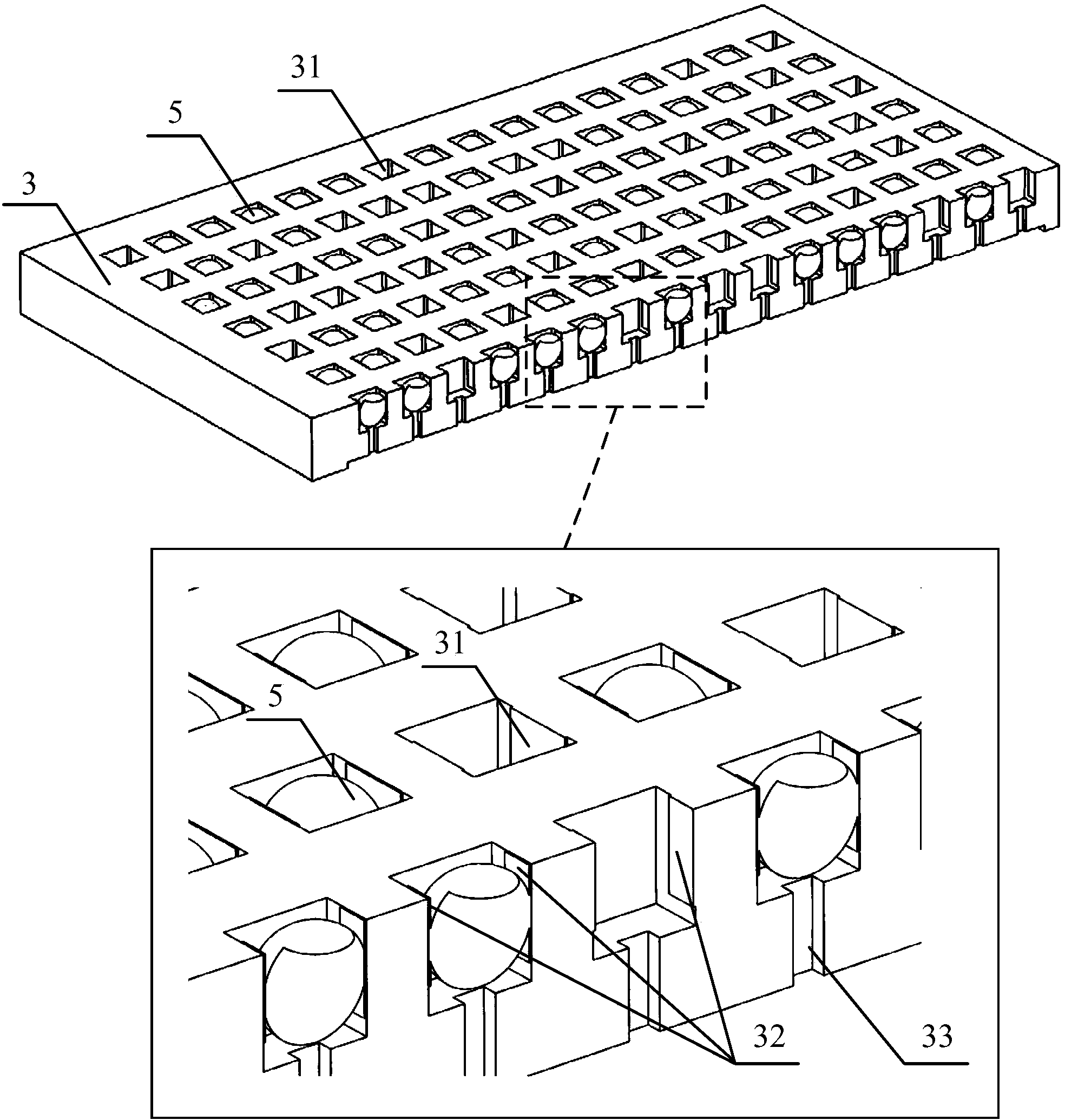

[0074] Substrate with silicon microhole array: N-type 4-inch silicon wafer is used, which is oxidized by wet method to form a 0.5 micron thick oxide layer on the ...

Embodiment 2

[0079] Transparent top cover and microfluidic channel: N-type 4-inch silicon wafer is used. After the planar shape of the microfluidic channel is photoetched, a 30-micron deep groove is etched using ICP dry method. Pour liquid PDMS into the tank, take it out after solidification, and cut it into rectangular pieces according to the dimensions of 2 cm long and 1 cm wide, and use a drill to drill holes at the required positions to form inflow holes and outflow holes, so that A one-piece transparent top cover and microfluidic channels were obtained.

[0080] Substrate with silicon microhole array: N-type 4-inch silicon wafer is used, and chemical vapor deposition (CVD) is used to form a 2 micron thick oxide layer on the surface of the silicon wafer, and microholes are photoetched on the front side of the silicon wafer At the plane position, the micropores are etched 30 microns deep by ICP dry etching. A 0.1-micron-thick chromium metal layer is sputtered on the front side of the s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Side length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More