Grid-controlled vertical double-diffusion metal-oxide semiconductor field effect transistor

A gate oxide layer and gate technology, which is applied to semiconductor devices, electrical components, circuits, etc., can solve the problems of large cell size, insufficient cell density, and high power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

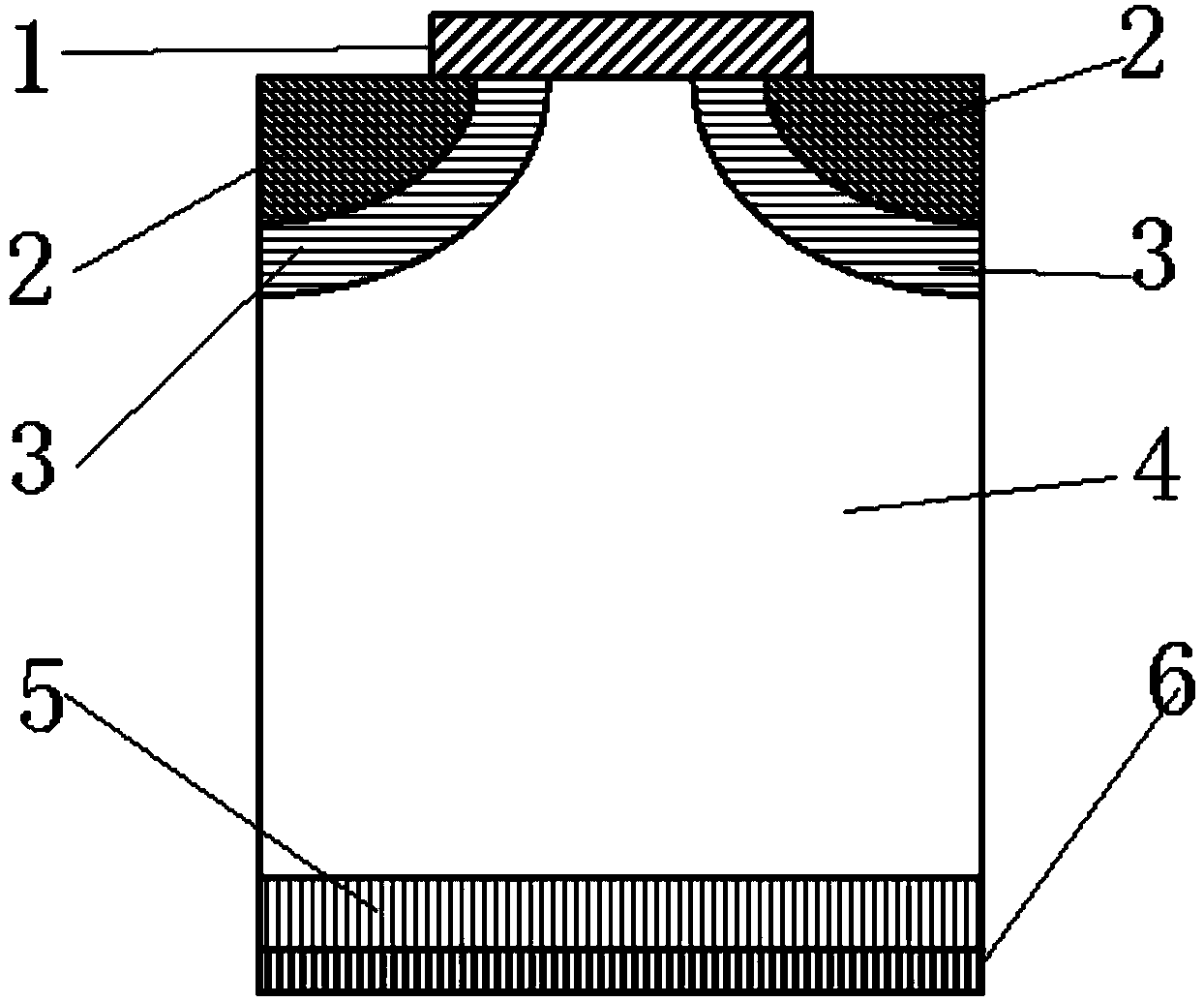

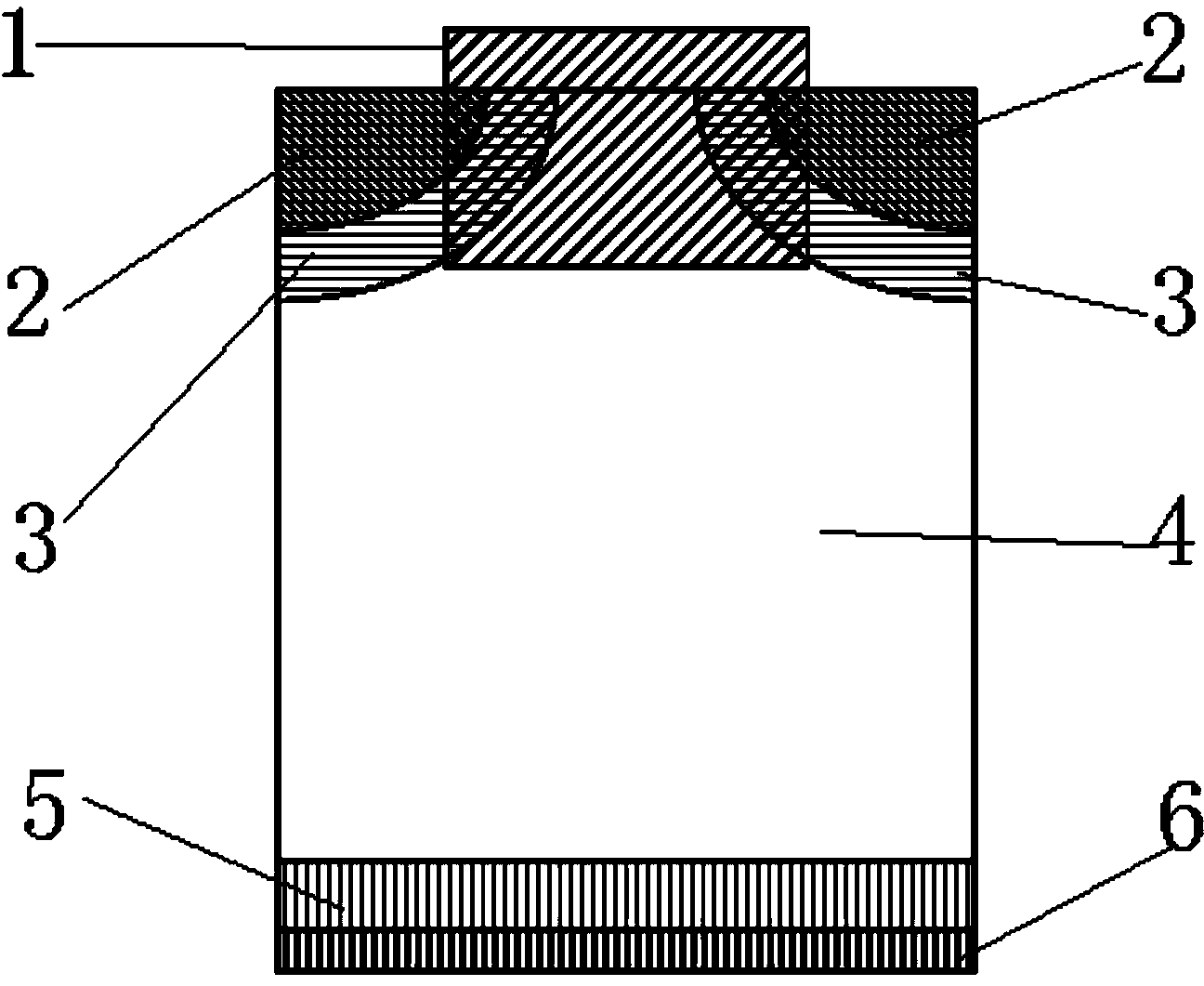

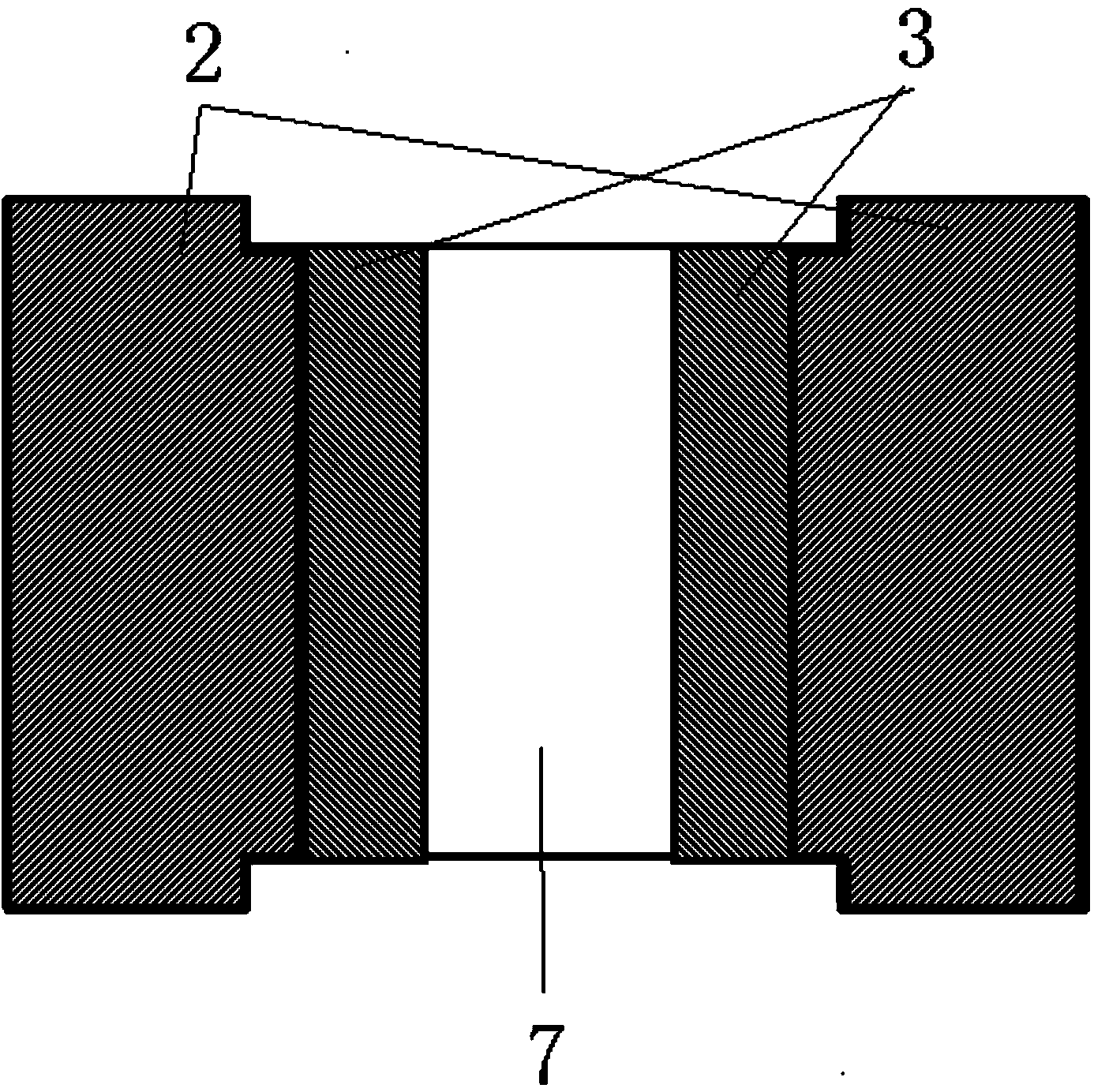

[0028] Take N-channel VDMOS device as an example, such as figure 2 As shown, it includes gate 1, N+ source region 2, P-type base region 3, N-drift region 4, N+ substrate 5, drain 6, and its gate 1 (across the gate oxide layer) covers the transistor. The channel region and the JFET region are from the top surface and the front and rear sides. During forward conduction, under the action of the gate voltage, the extended gate electrode makes both the channel region and the JFET region generate a charge accumulation layer, which can significantly reduce the on-resistance and increase the output current. Moreover, due to the ability of the folded gate to control the charge of the JFET region, the punch-through problem caused by the reduced size of the JFET region can be avoided, thereby promoting the charge sharing effect of the cells, opt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More