Manufacturing method of surface-plasmon-enhanced GaN-based nanopore LED

A surface plasmon and nanopore technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of difficulty in achieving luminous efficiency, low material growth quality, and large LED turn-on voltage, and achieves close coupling distance, Good electrical properties and enhanced luminous efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

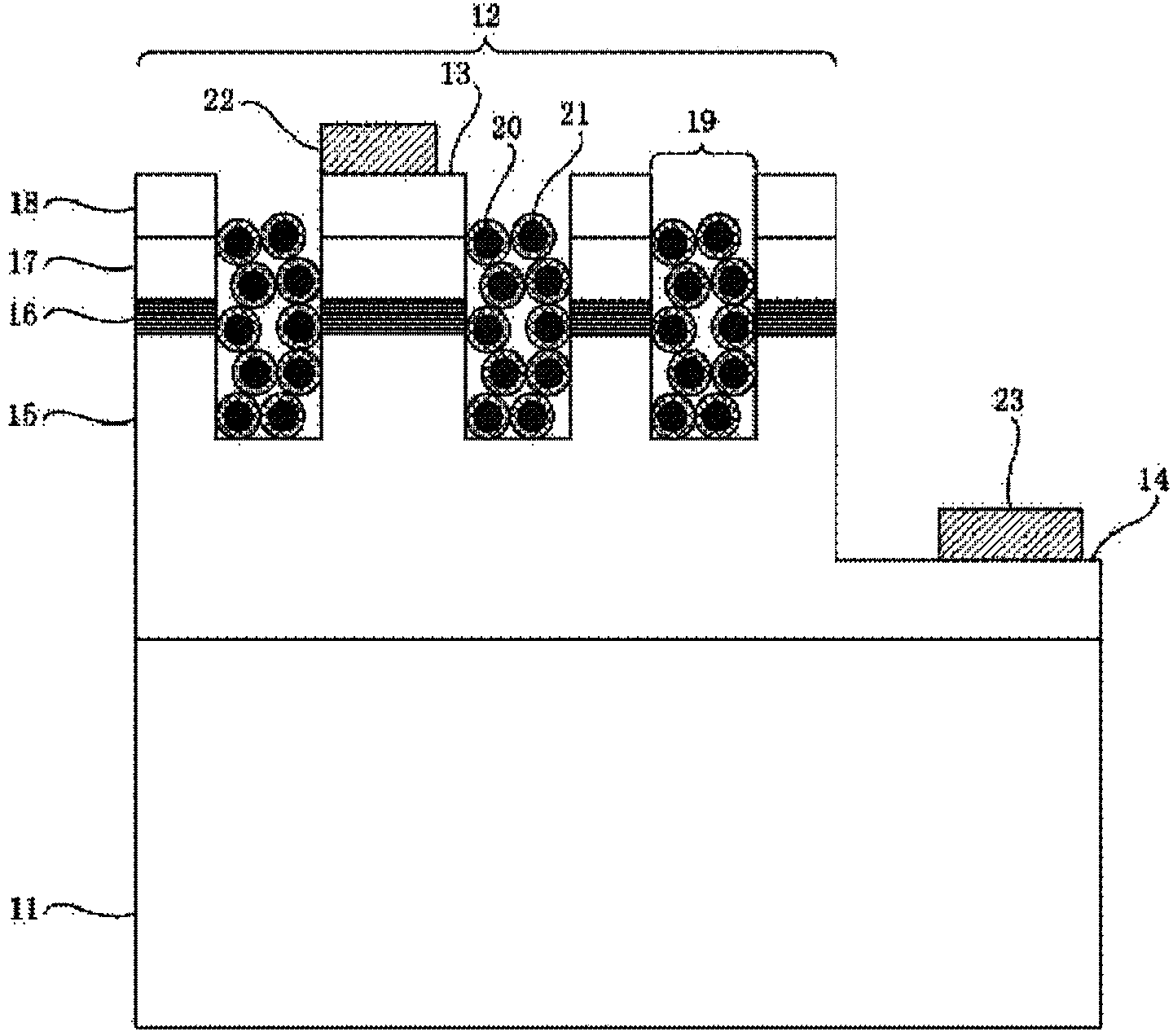

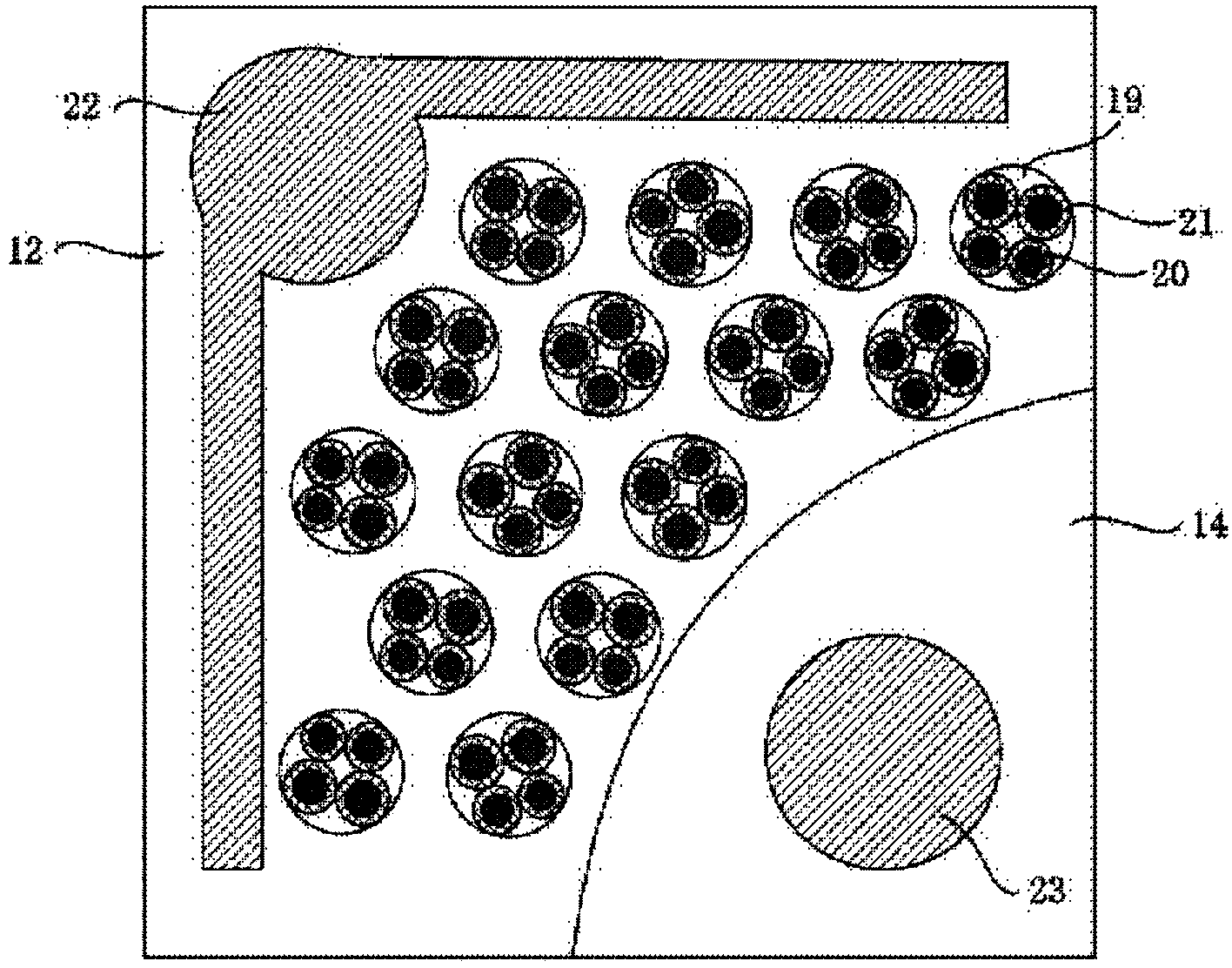

[0017] see figure 1 and figure 2 , the invention provides a method for preparing a surface plasmon-enhanced GaN-based nanohole LED, comprising the following steps:

[0018] Step 1: sequentially grow n-type In on the substrate 11 x Al y Ga z N 1-x-y-z (0≤x, y, z≤1) layer 15, undoped or doped multiple quantum well layer 16, p-type In x Al y Ga z N 1-x-y-z (0≤x, y, z≤1) layer 17 and current spreading layer 18, the material of described substrate 11 is sapphire, silicon, silicon carbide, GaN or glass, the material of described multiple quantum well layer 16 is InAlGaN / InAlGaN, the period is 2-10, and the material of the current spreading layer 18 is ITO, single-layer or multi-layer graphene;

[0019] Step 2: use photolithography and dry etching process to etch downward on the current spreading layer 18, and the etching depth reaches n-type In x Al y Ga z N 1-x-y-z (0≤x, y, z≤1) layer 15 to form a GaN-based LED structure nanohole array 12, the nanohole depth of the Ga...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More