Low-temperature poly-silicon TFT array substrate, manufacturing method thereof and display device

A low-temperature polysilicon and polysilicon technology, used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of complex preparation process, high preparation cost, low process yield, etc., to improve process yield, reduce Process cost and the effect of reducing process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

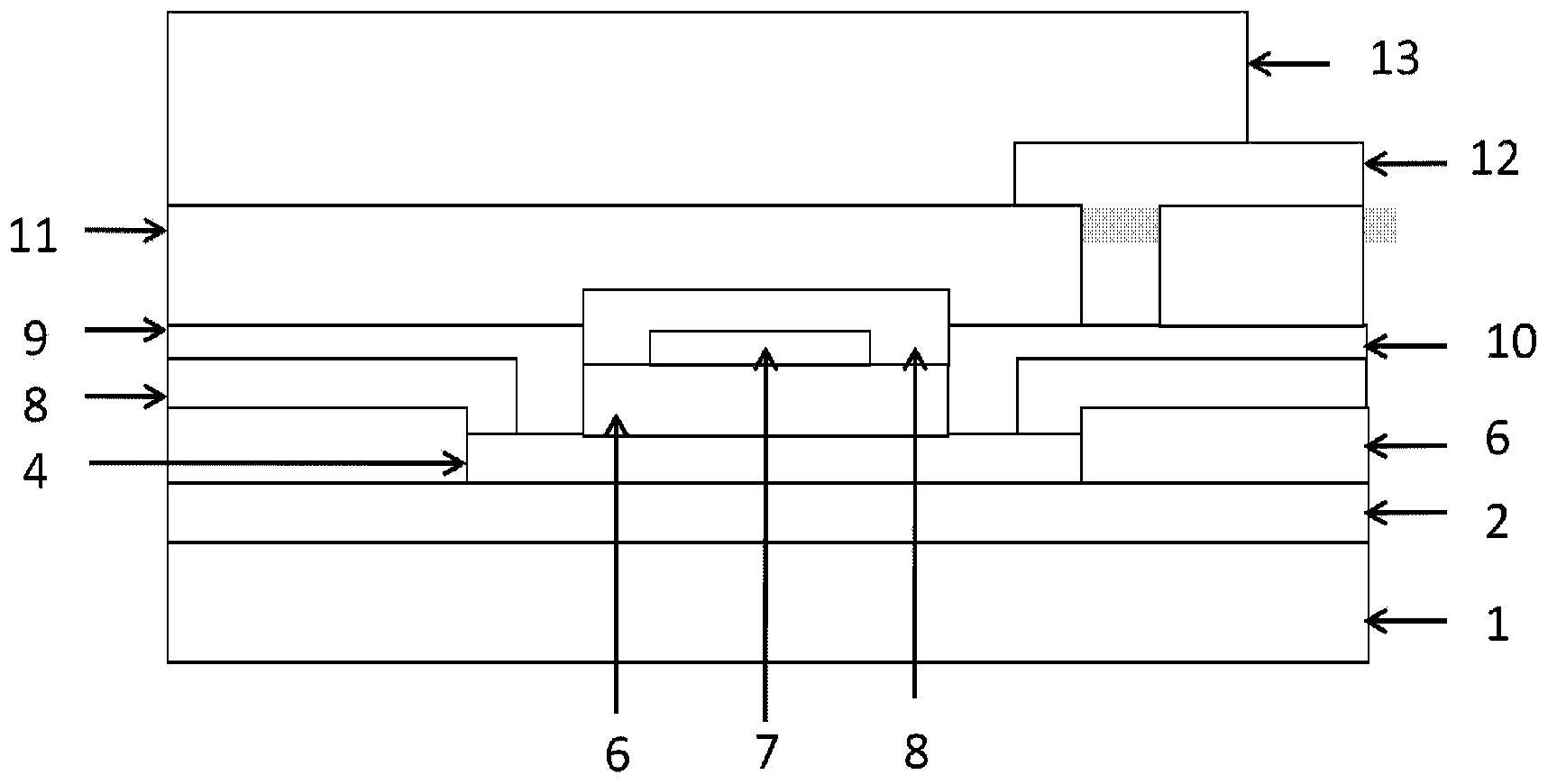

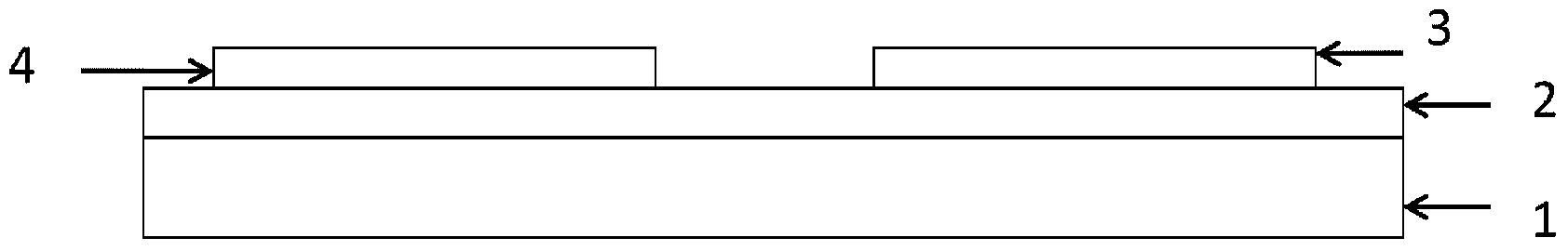

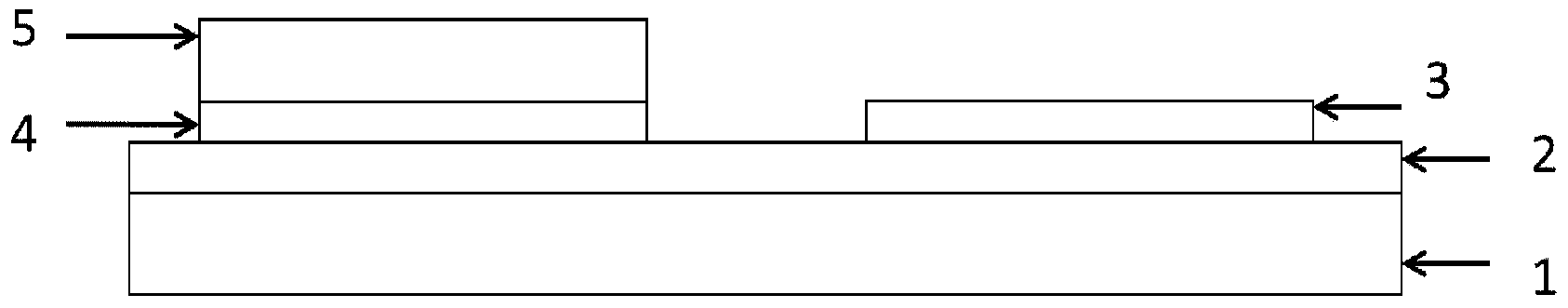

[0042] According to one aspect of the present invention, in order to reduce the number of photolithography in the process of preparing a low-temperature polysilicon thin-film field-effect transistor array substrate, the present invention provides a method for preparing a low-temperature polysilicon thin-film field-effect transistor array substrate. The method uses three process technologies , that is: semi-transparent mask plate masking process, film lift-off process, and gate (gate line) and source-drain electrode (data line) deposition on the same layer, so that the number of photolithography processes for preparing low-temperature polysilicon thin film field effect transistor array substrate Down to 4 times. Among them...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More