Formation method of transistor

A technology for transistors and layer formation, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as poor transistor performance, and achieve the effect of promoting progress, reducing gate leakage current, and reducing thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

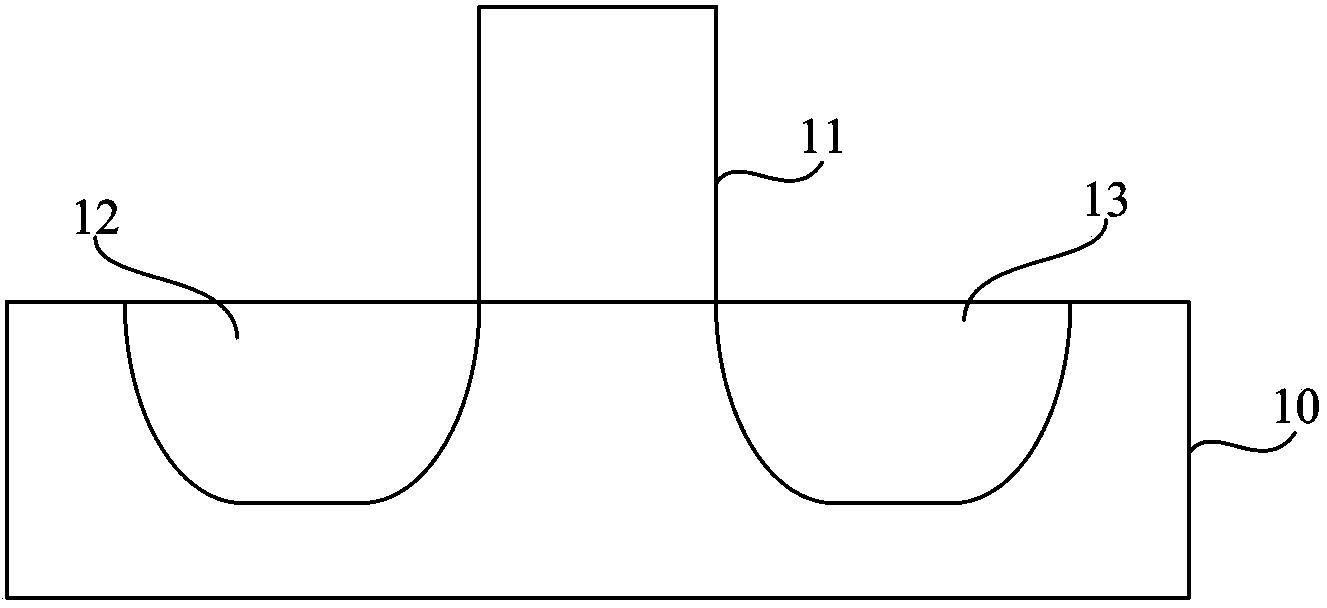

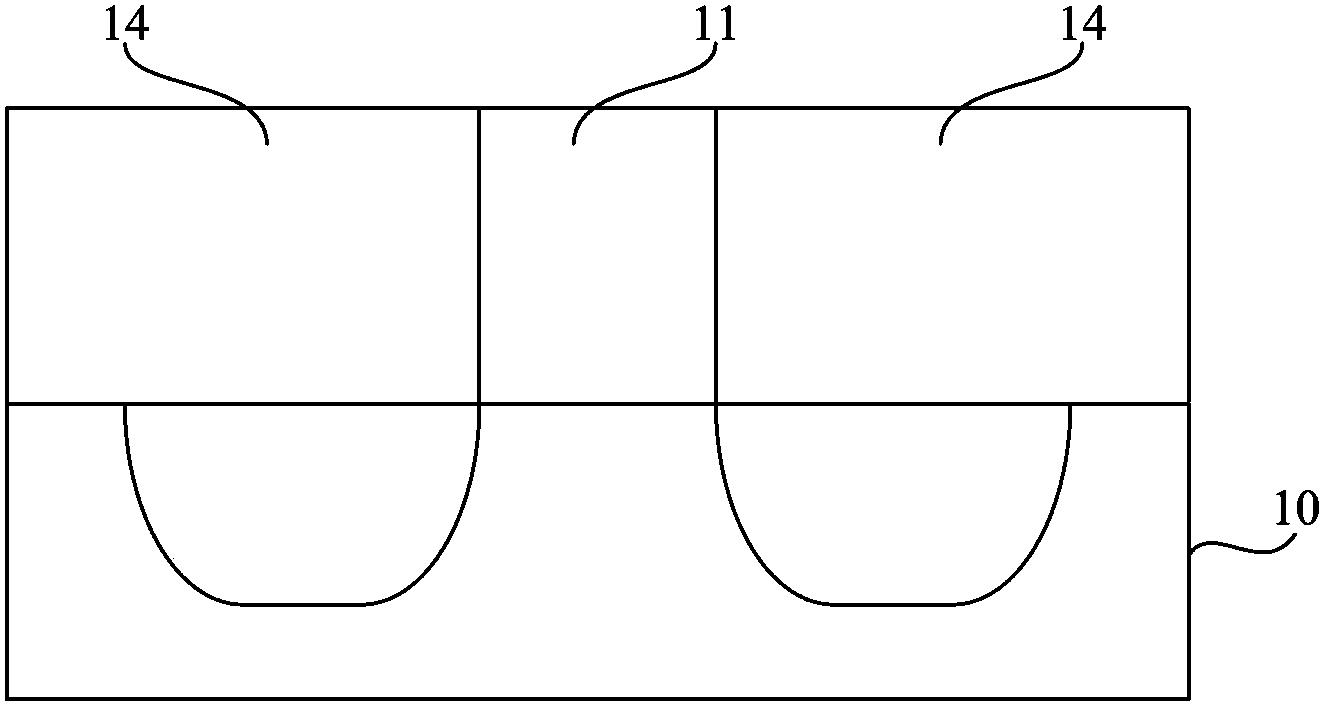

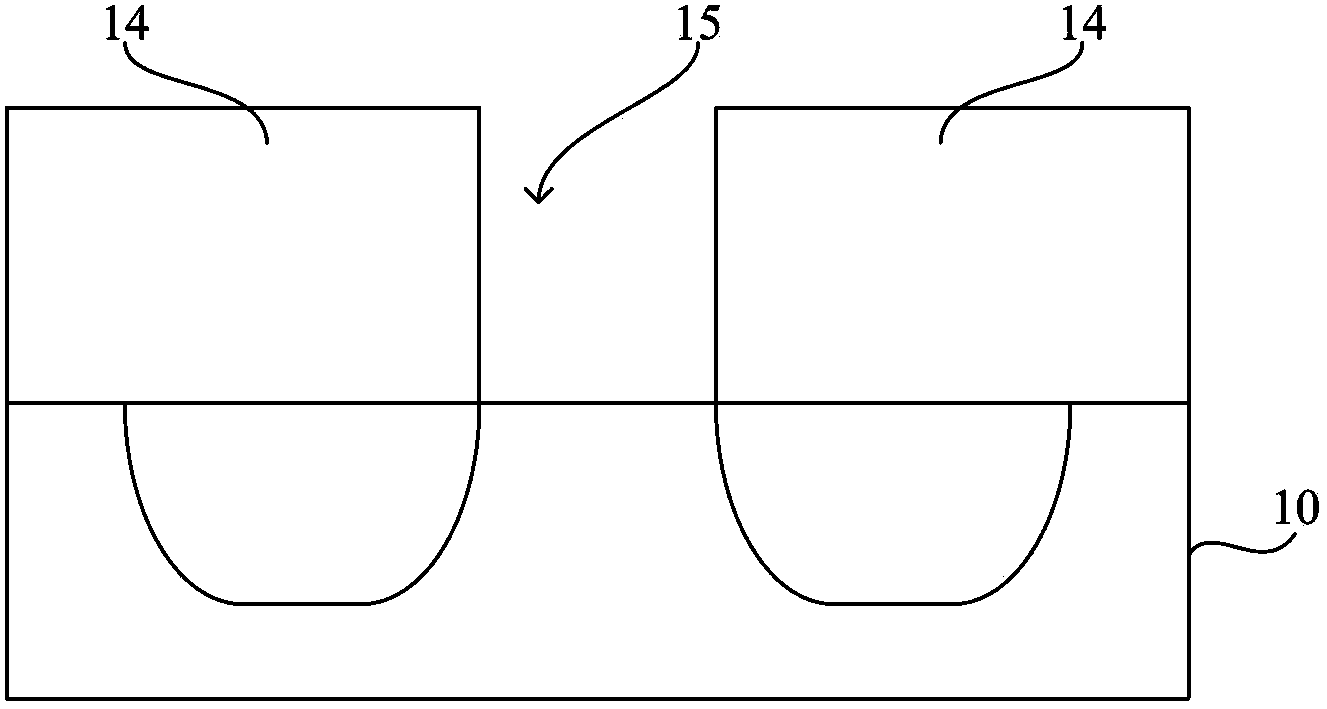

[0042] The inventor has conducted research on the problems existing in the prior art and found that: with reference to Figure 5 , the method of forming the work function adjustment layer on the high-K gate dielectric layer usually uses a sputtering process, and the sputtered ions will diffuse into the high-K gate dielectric layer in large quantities, and this diffusion is random, and then in the high-K gate dielectric layer inhomogeneous doping. This makes the threshold voltage of the metal gate of the transistor different at different positions in the gate length direction, which affects the performance of the transistor. Moreover, since this diffusion is random, there is a possibility that sputtered ions diffuse through the high-K gate dielectric layer and enter the substrate, resulting in higher metal gate leakage current of the transistor. These factors significantly reduce the effect of the high-K gate dielectric layer, thereby reducing the performance of the transistor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More