Simple Charge Pump Circuit for Low Voltage Operation

A charge pump and low-voltage technology, which is applied in the field of semiconductor integrated circuits, can solve the problems of complicated circuit implementation, shortened effective opening time of M0, occupied charge transfer time, etc., and achieves reduced layout area, simplified circuit and layout structure, and reduced reverse current Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

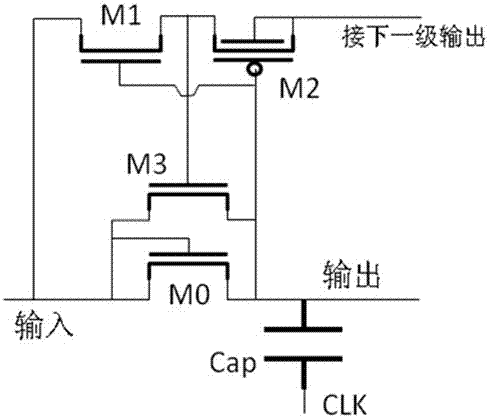

[0027] For the technical means that the present invention realizes, feature and effect are easy to understand, combine below Figure 6 and Figure 7 for further clarification. These descriptions and illustrations of embodiments should not be construed as limitations of the present invention. Obvious changes to the characteristics of the examples of the present invention and the extension of its application principles will also fall within the protection scope of the present invention.

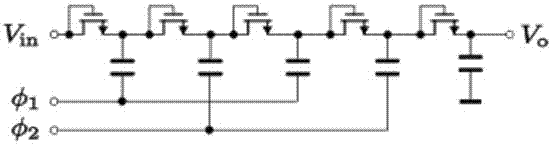

[0028] A simple charge pump circuit provided by the present invention is an improvement to the Dickson charge pump circuit, which can provide the required operating voltage for non-volatile memory integrated circuits, such as being used in EEPROM or flash memory chips, to generate by low voltage operation High voltage required for programming and erasing.

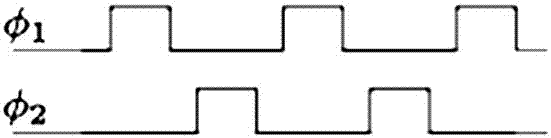

[0029] The simple charge pump circuit suitable for low-voltage operation provided by the present invention includes several charge pump ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More