Method for manufacturing gate insulation layer

A gate insulating layer and gate technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increased impedance, high leakage current, and poor barrier effect of alkali metal ions, so as to improve the equivalent capacitance , Reduce leakage current, enhance the effect of anti-static discharge (ESD) ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] Put the Cu grid into a vacuum chamber, and pass H into it successively under the condition of 0 power 2 with N 2 , where H 2 The flow rate is 5000sccm, the passage time is 10 seconds, N 2 The flow rate is 5000 sccm, the passage time is 10 seconds, and then vacuum treatment is carried out.

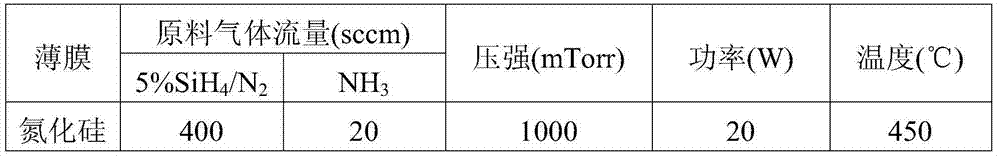

[0036] In a vacuum chamber, the plasma-enhanced chemical vapor deposition method was used to deposit a thickness of 500 Å on the surface of the Cu gate using the Oxford Instrument Plasma80Plus system. The silicon nitride layer, the raw material gas is SiH 4 with N 2 Mixed gas and NH 3 , SiH 4 with N 2 The flow rate of mixed gas is 400sccm, where SiH 4 The mass fraction is 5%, NH 3 The flow rate is 20 sccm, and the specific deposition process parameters are shown in Table 1.

[0037] Table 1

[0038]

[0039] Then, in another chamber, the deposited silicon nitride layer is heated at 500° C. for 40 minutes for dehydrogenation.

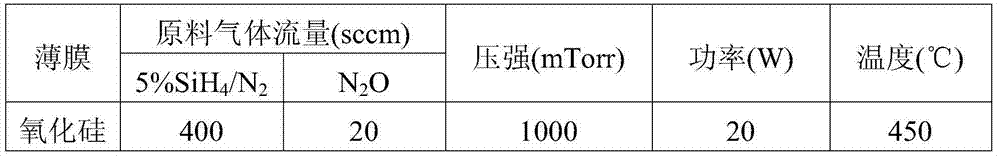

[0040] In a vacuum chamber, the plasma-en...

Embodiment 2

[0045] Put the Cu grid into a vacuum chamber, and pass H into it successively under the condition of 0 power 2 with N 2 , where H 2 The flow rate is 6000sccm, the access time is 8 seconds, N 2 The flow rate is 6000 sccm, the passage time is 8 seconds, and then the vacuum treatment is carried out.

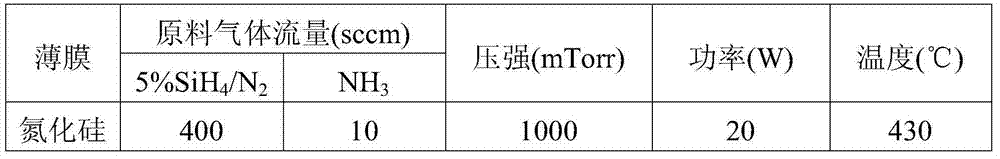

[0046] In a vacuum chamber, the plasma-enhanced chemical vapor deposition method was used to deposit a thickness of 600 on the surface of the Cu gate using the Oxford Instrument Plasma80Plus system. The silicon nitride layer, the raw material gas is SiH 4 with N 2 Mixed gas and NH 3 , SiH 4 with N 2 The flow rate of mixed gas is 400sccm, where SiH 4 The mass fraction is 5%, NH 3 The flow rate is 10 sccm, and the specific deposition process parameters are shown in Table 3.

[0047] table 3

[0048]

[0049] Then, in another chamber, the deposited silicon nitride layer was heated at 450° C. for 50 minutes for dehydrogenation.

[0050] In a vacuum chamber, the plasma-en...

Embodiment 3

[0055] Put the Cu grid into a vacuum chamber, and pass H into it successively under the condition of 0 power 2 with N 2 , where H 2 The flow rate is 8000sccm, the access time is 5 seconds, N 2 The flow rate is 8000 sccm, the passage time is 5 seconds, and then the vacuum treatment is carried out.

[0056] In a vacuum chamber, the plasma-enhanced chemical vapor deposition method was used to deposit a thickness of 700 on the surface of the Cu gate using the Oxford Instrument Plasma80Plus system. The silicon nitride layer, the raw material gas is SiH 4 with N 2 Mixed gas and NH 3 , SiH 4 with N 2 The flow rate of mixed gas is 600sccm, in which SiH 4 The mass fraction is 5%, NH 3 The flow rate is 10 sccm, and the specific deposition process parameters are shown in Table 5.

[0057] table 5

[0058]

[0059] Then, in another chamber, the deposited silicon nitride layer was heated at 550° C. for 30 minutes for dehydrogenation.

[0060] In a vacuum chamber, the plasma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More