A method for preparing 10nm T-grid by electron beam exposure

A technology of electron beam exposure and electron beam lithography, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problem of poor conformality of etched topography and poor resistance of photoresist to plasma etching , development process requirements are very high, etc., to achieve the effect of small etching size, reduced size, and high thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0044] The present invention is to fabricate a nanometer T-shaped gate structure on the device substrate as a gate, use electron beam lithography and reactive ion etching to form a T-shaped shape with a size of 10nm, and use thermal evaporation to evaporate the gate metal and peel off to obtain a T-shaped structure with a size of 10nm. The metal gate is compatible with the basic process for preparing HEMT devices, and can greatly reduce the size of the T-shaped gate.

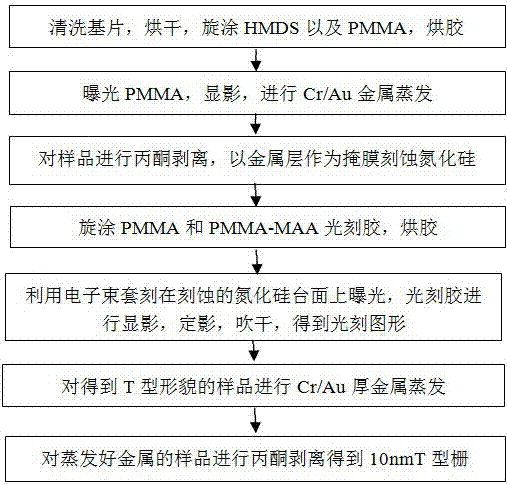

[0045] Figure 2-Figure 8 It is a flow chart of a method for preparing a 10nm T-shaped grid by electron beam lithography and reactive ion etching provided by the present invention, the method comprising:

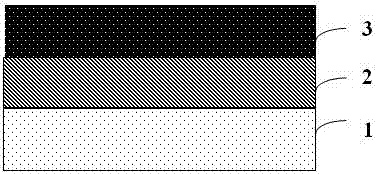

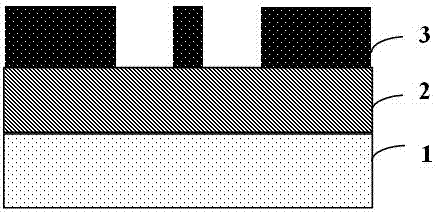

[0046] Step 1: If figure 2 As shown, electron be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More