Semiconductor device, preparation method and packaging method thereof

A packaging method and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems affecting wafer bonding strength, etc., to improve weak current problems, improve bonding quality, Effect of improving package reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

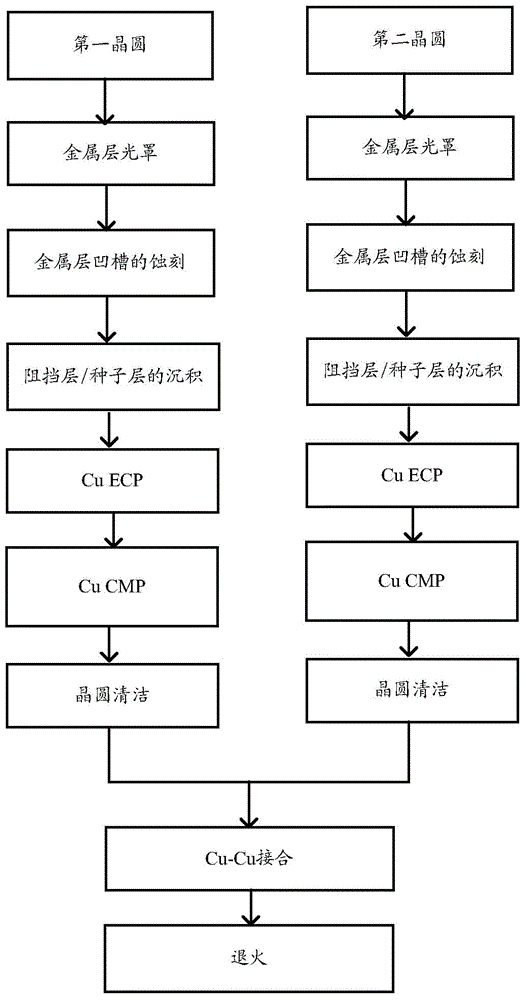

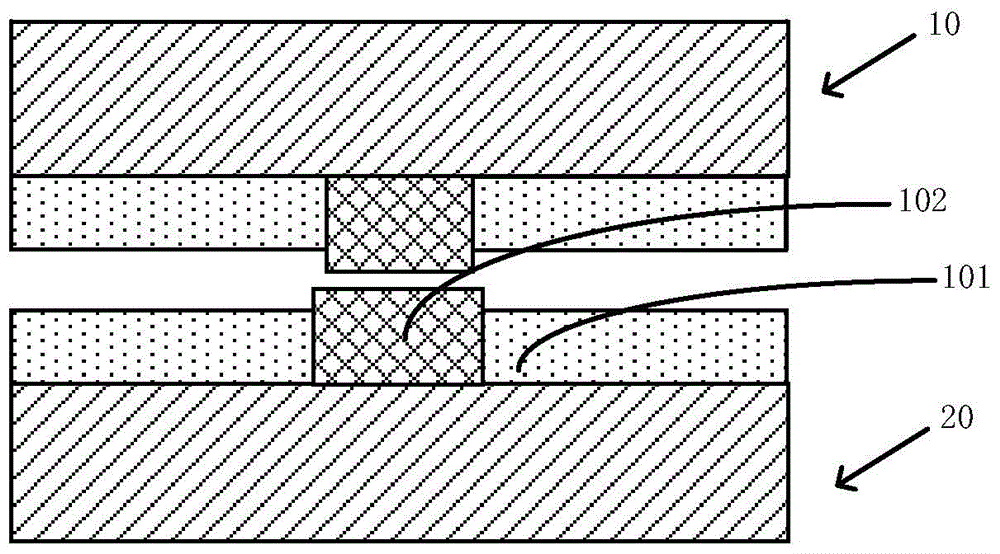

[0057] In order to solve the problems existing in the current wafer bonding process, the present invention provides a method for preparing and packaging a semiconductor device. Figure 4-5 The method is described further.

[0058] in, Figure 4 The process flow chart of bonding two wafers in the present invention; Figure 5 It is a schematic diagram of a partial structure of bonding two wafers in a specific embodiment of the present invention.

[0059] Firstly, step 201 is executed to provide a substrate 201 .

[0060] Specifically, refer to Figure 5 , in this step, the base 201 includes at least a substrate, and the substrate may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), stacked silicon-on-insulator (SSOI), Silicon germanium on insulator (S-SiGeOI) and silicon germanium on insulator (SiGeOI) are laminated.

[0061] Optionally, components and interconnection structures may also be formed on the substrate 201 .

[0062] Step 2...

Embodiment 2

[0109] The present invention also provides a semiconductor device, which is prepared by the method described in Embodiment 1. The semiconductor device prepared by the method can realize the hermetic bonding of the bonding pad, increase the bonding strength (bondingstrength), and improve the bonding quality of the wafer; using an insulating AD-BCB material for auxiliary bonding can improve The weak current problem between the joint copper pillars (Cupillar) improves the electrical stability; the use of hybrid bonding (hybrid bonding) can greatly improve the reliability of the package and the life of the chip.

Embodiment 3

[0111] The present invention also provides an electronic device, including the semiconductor device described in Embodiment 2. Wherein, the semiconductor device is the semiconductor device described in Embodiment 3, or the semiconductor device obtained according to the preparation method described in Embodiment 1.

[0112] The electronic device of this embodiment can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV set, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. , can also be any intermediate product including the semiconductor device. The electronic device according to the embodiment of the present invention has better performance due to the use of the above-mentioned semiconductor device.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More