HVMOS integrated with demagnetization sampling device, and demagnetization sampling circuit

A demagnetization sampling and device technology, applied in the field of HVMOS, can solve the problems that the chip demagnetization signal feedback port is susceptible to interference, increase system cost, waste chip area, etc., to save auxiliary windings and voltage divider resistors, reduce system cost, reduce Die area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

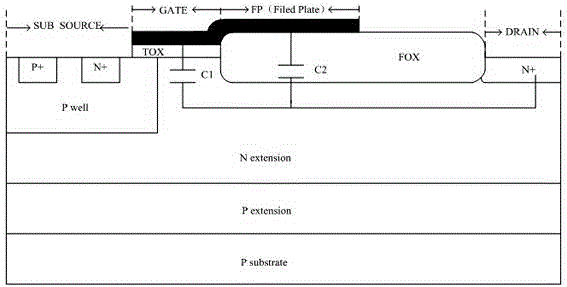

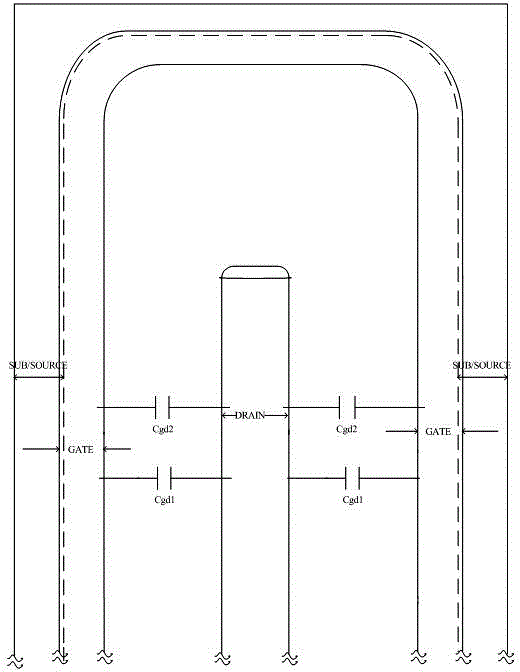

[0055] The cross-sectional schematic diagram of the cell structure of an LDMOS high-voltage device integrating independent high-voltage covering capacitors is shown in Figure 6 shown. Compared with the traditional LDMOS, the new structure is a five-terminal device with DRAIN, GATE, SOURCE, SUBSTRATE, and FP. Compared with traditional LDMOS, FP and GATE are disconnected to form both ends of LDMOS.

[0056] (1) The Cgd capacitor is composed of the GATE plate through the TOX (gate oxide layer) medium at the end of the channel, passing through the drift region and the drain (DRAIN) plate. Cgd is still in series with Cgs and Cgb, and is still affected by the Miller effect when applied.

[0057] (2) The CHV capacitor is formed between the FP plate passing through the FOX (field oxide layer) medium, passing through the drift region and the drain (DRAIN) plate. The FP field plate is POLY (polysilicon gate), and the drain (DRAIN) terminal is metal and semiconductor to form an ohmic...

Embodiment 2

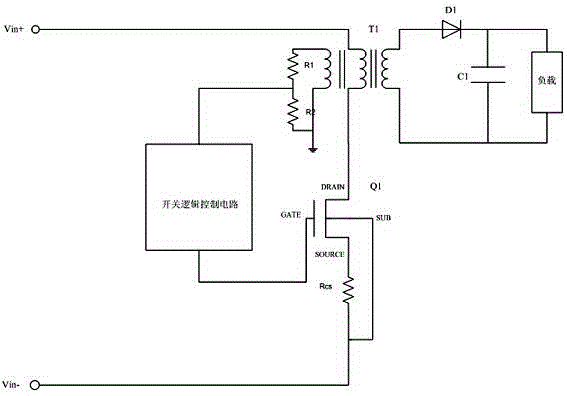

[0061] Embodiment 2 of the present invention proposes a circuit for demagnetization sampling using an HVMOS integrated demagnetization sampling device such as Figure 9 shown. The traditional demagnetization sampling circuit such as image 3 , Figure 4 shown. Traditional demagnetization sampling circuits require additional demagnetization sampling devices when detecting demagnetization. The demagnetization sampling circuit of the present invention includes an output rectifier circuit, a transformer T1, an integrated high-voltage capacitor LDMOS device Q1, a demagnetization signal sampling circuit 2, a demagnetization time timing circuit 3, and a switch logic control circuit 4.

[0062] One end of the primary of the transformer T1 is connected to the input Vin+, and the other end of the primary of the transformer T1 is connected to the drain (DRAIN) end of the switching device LDMOS. One end of the transformer T1 secondary is connected to the positive pole of the diode D1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com