Preparation technology of silicon micro wire array

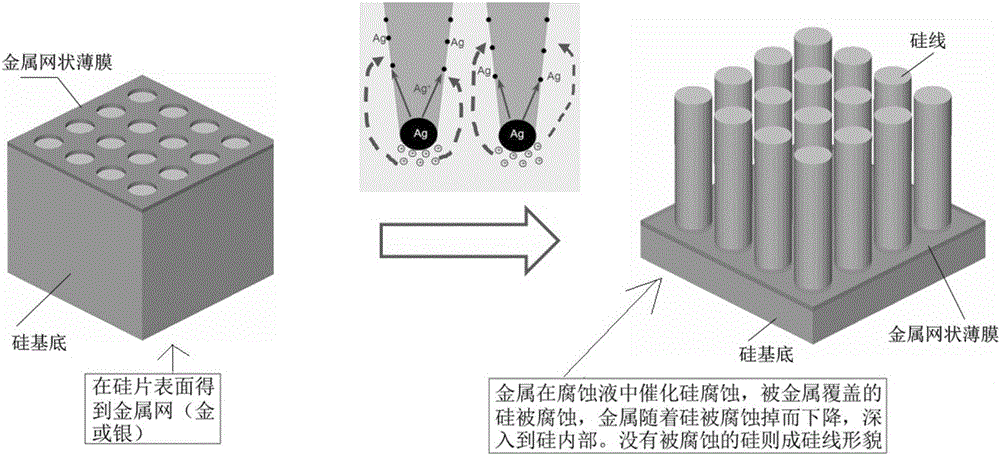

A preparation process and technology of micro-wires, applied in the fields of nanotechnology, nanotechnology, semiconductor/solid-state device manufacturing, etc., can solve the problem of high surface defect density, silicon micro-wire spacing, small aspect ratio, limiting the application of silicon micro-nano structures and other problems, to achieve the effect of large aspect ratio and good adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

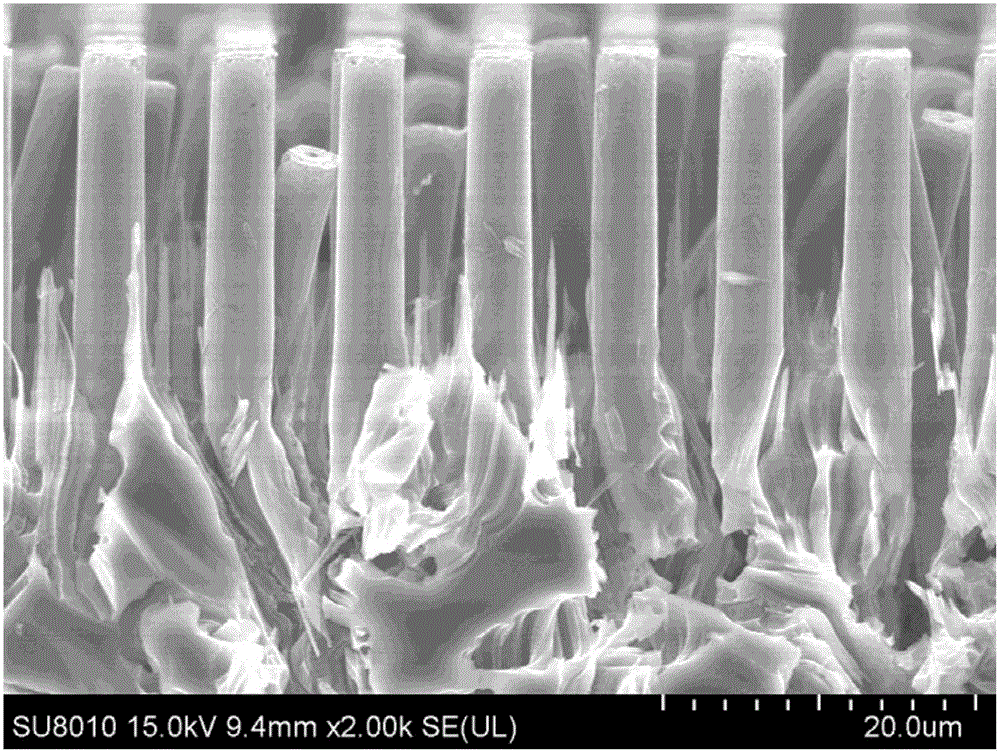

Examples

Embodiment 1

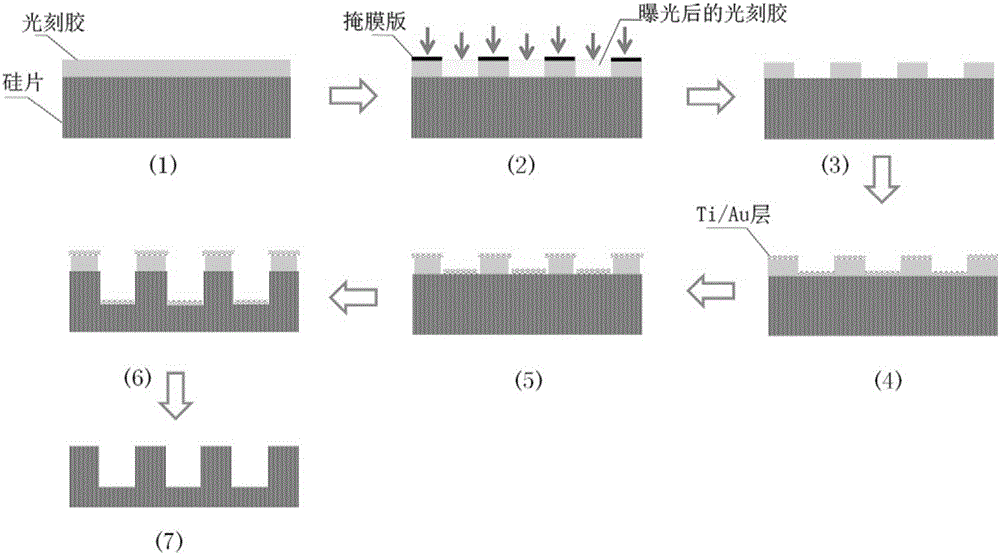

[0050] (1) Dry silicon wafers that have been ultrasonically cleaned with acetone, ethanol, and deionized water; drop RZJ304 photoresist, rotate at 5000rpm for 40 seconds, and then bake on a 100°C hot plate for 100 seconds;

[0051] (2) Press the photolithographic mask plate on the silicon wafer coated with photoresist in a soft contact method, and expose it to ultraviolet light for 8 seconds; wherein, the light-shielding area in the photolithographic plate is a square array of dots, with a diameter of 4 μm and a periodicity 8 μm in length;

[0052] (3) Develop in RZX-3038 developer for 30 seconds, take out and dry; obtain a photoresist cylinder array with a period of 8 μm and a diameter, diameter and interval of 4 μm;

[0053] (4) 5nm Ti and 40nm Au were deposited successively by electron beam evaporation technology, and the deposition rates were respectively and

[0054] (5) Soak in acetone and shake slightly for 1 minute;

[0055] (6) Configure HF and H 2 o 2 Mix the...

Embodiment 2

[0059] (1) Dry the silicon wafers that have been ultrasonically cleaned with acetone, ethanol and deionized water respectively. Drop RZJ304 photoresist, rotate at 5000rpm for 40 seconds, and then bake on a 100°C hot plate for 100 seconds;

[0060] (2) Press the photolithographic mask plate on the silicon wafer coated with photoresist in a soft contact method, and expose it to ultraviolet light for 8 seconds; wherein, the light-shielding area in the photolithographic plate is a square array of dots, with a diameter of 3 μm and a periodicity 8 μm in length;

[0061] (3) Develop in RZX-3038 developer solution for 30 seconds, take out and dry; obtain a photoresist cylinder array with a period of 8 μm, a diameter of 3 μm, and an interval of 5 μm;

[0062] (4) 5nm Ti and 40nm Au were deposited successively by electron beam evaporation technology, and the deposition rates were respectively and

[0063] (5) Soak in acetone and shake slightly for 1 minute;

[0064] (6) Configure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More