Formation method of semiconductor device

A semiconductor and device technology, which is applied in the field of semiconductor device formation, can solve problems such as etching damage, low overall performance of semiconductor devices, and the second metal gate is easily corroded, so as to achieve the effect of avoiding corrosion and preventing corrosion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] It can be seen from the background art that the electrical performance of semiconductor devices formed in the prior art needs to be improved.

[0034]It has been found through research that in order to meet the requirements of improving the threshold voltage (ThresholdVoltage) of NMOS tubes and PMOS tubes at the same time, different metal materials are usually used as the work function (WF, WorkFunction) layer materials of the metal gates of NMOS tubes and PMOS tubes, so NMOS tubes The metal gates of the NMOS transistor and the PMOS transistor are formed successively, instead of forming the metal gates of the NMOS transistor and the PMOS transistor at the same time.

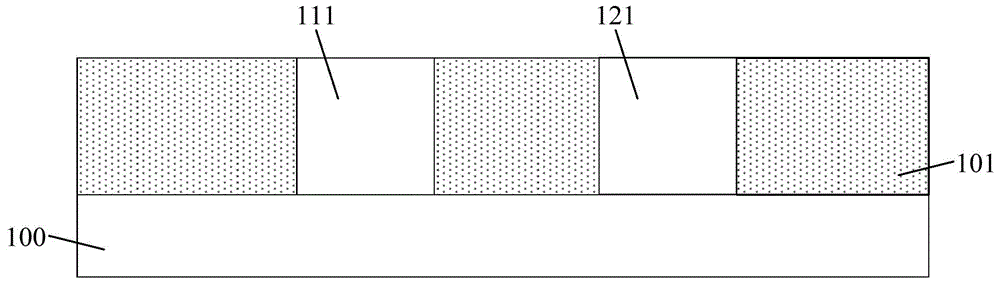

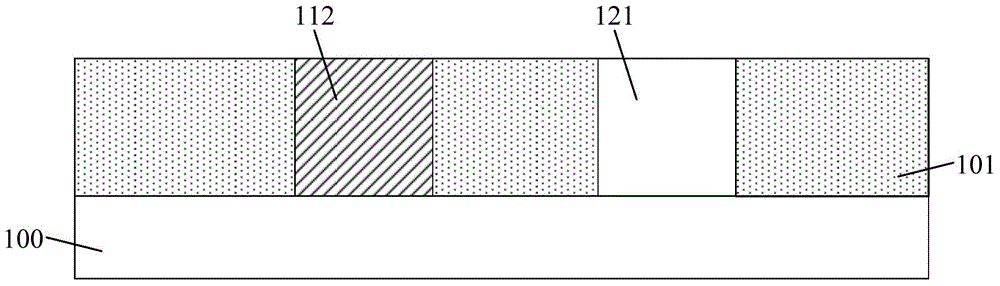

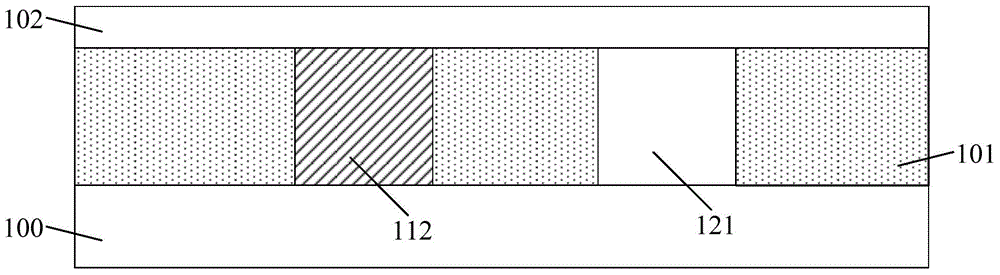

[0035] In one embodiment, refer to figure 1 , providing a substrate 100, the substrate 100 includes a PMOS region, an NMOS region and other device regions; a first dummy gate 111 is formed on the substrate 100 in the NMOS region, and a second dummy gate 121 is formed on the substrate 100 in the PMOS regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More