Chip packaging structure for slowing down electromagnetic interference and packaging method

A chip packaging structure, electromagnetic interference technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of affecting signal transmission quality, line impedance mismatch, line noise increase, etc., to reduce the signal between lines inside the chip crosstalk, improved packaging reliability, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

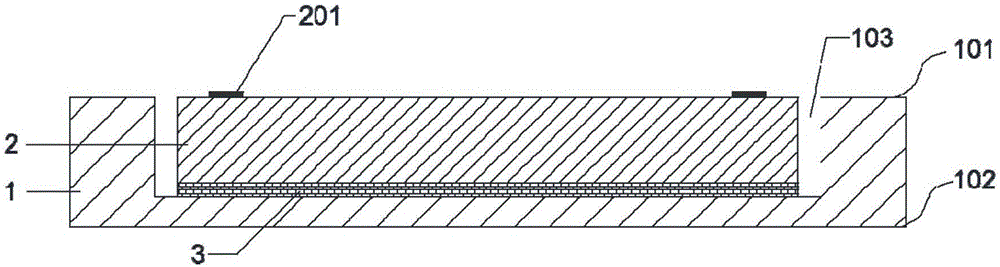

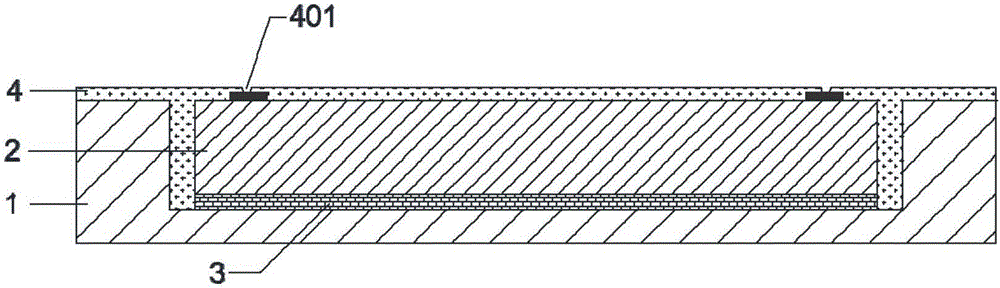

[0055] like Figure 11 and Figure 12 As shown, a chip packaging structure for mitigating electromagnetic interference includes a silicon substrate 1 and a chip 2, the silicon substrate has a first surface 101 and a second surface 102 opposite to it, and at least A sinking groove 103 facing the second surface, the sinking groove is preferably a straight groove or an inclined groove with an angle between the side wall and the bottom surface of 80-120, which is not limited here. The schematic diagram of this embodiment is in the shape of a straight groove. At least one chip 2 can be placed in the sinking groove. In this embodiment, a chip is placed, and the front of the chip is close to the first surface; specifically, the back of the chip is pasted with an adhesive 3 Installed to the groove bottom of the sinking groove to realize chip mounting, to better fix the chip and prevent the chip from shifting. The front side of the chip includes a pad 201; a first insulating layer 4...

Embodiment 2

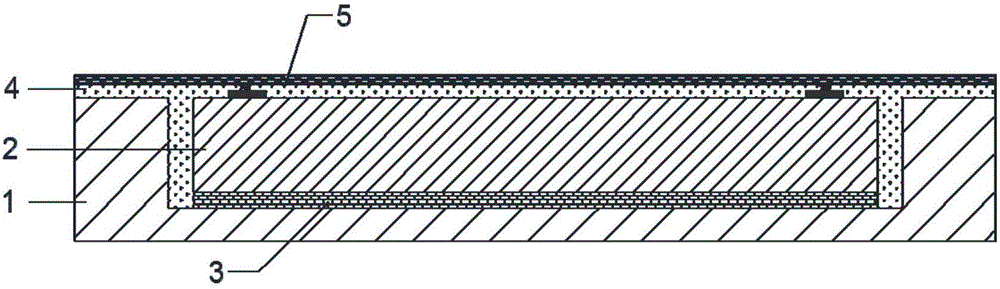

[0089] like Figure 13 and Figure 14 As shown, a chip packaging structure for mitigating electromagnetic interference includes a silicon substrate 1 and a chip 2. The silicon substrate has a first surface 101 and a second surface 102 opposite to it. The sunken groove 103 on the surface, at least one chip is mounted on the bottom of the sunken groove with the back facing down, and the front of the chip contains a solder pad 201; between the peripheral side of the chip and the side wall of the sunken groove, the front of the chip And the first insulating layer 4 is formed on the first surface; the first metal rewiring 501, the first inductance wiring 502 that goes around continuously, and at least two first capacitance wirings with a dielectric layer in between are formed on the first insulating layer. 503, the first metal rewiring, the first inductance wiring, and the first capacitor wiring are electrically connected to the pads of the chip through the first insulating layer;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More