MTM anti-fuse structure on through hole and preparation process thereof

A preparation process and anti-fuse technology, which is applied in the field of microelectronics, can solve problems such as increasing the lateral size of the anti-fuse structure, short-circuit failure of the upper and lower electrodes of the anti-fuse, and affecting the integration of anti-fuse units, so as to reduce overlay risk, elimination of short-circuit phenomenon, effect of size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described below in conjunction with specific drawings and embodiments.

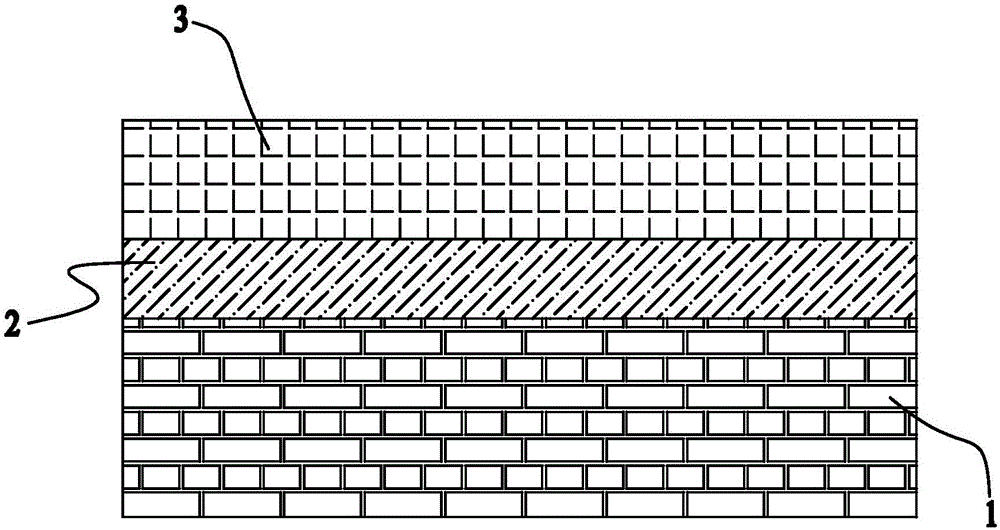

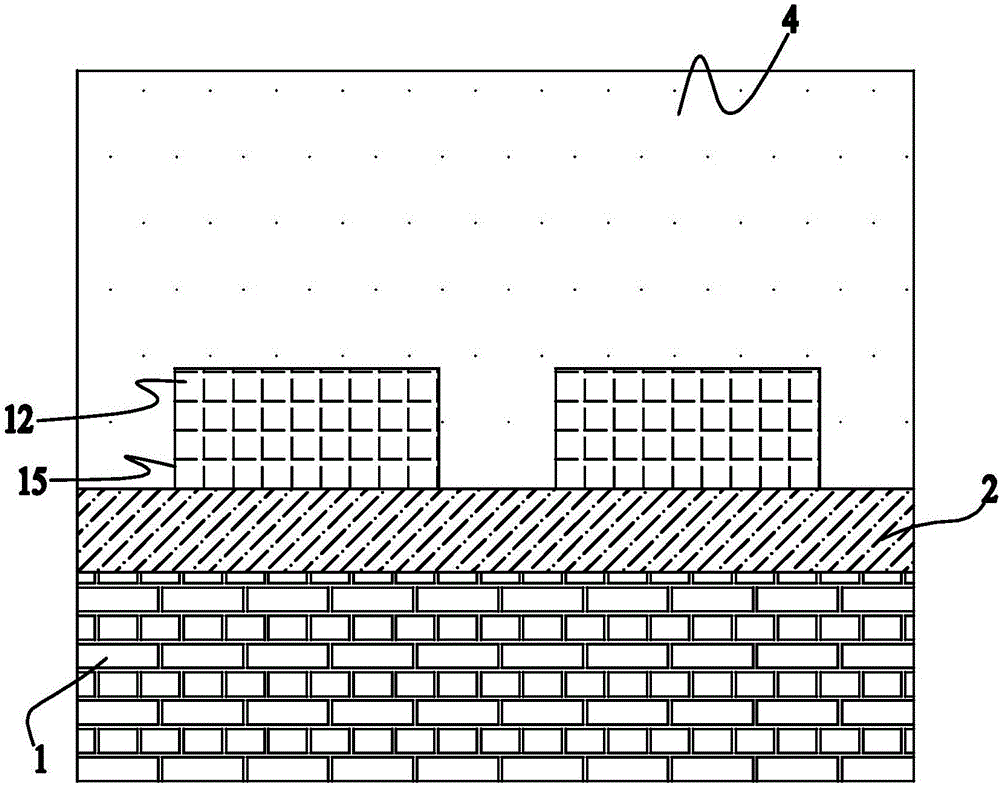

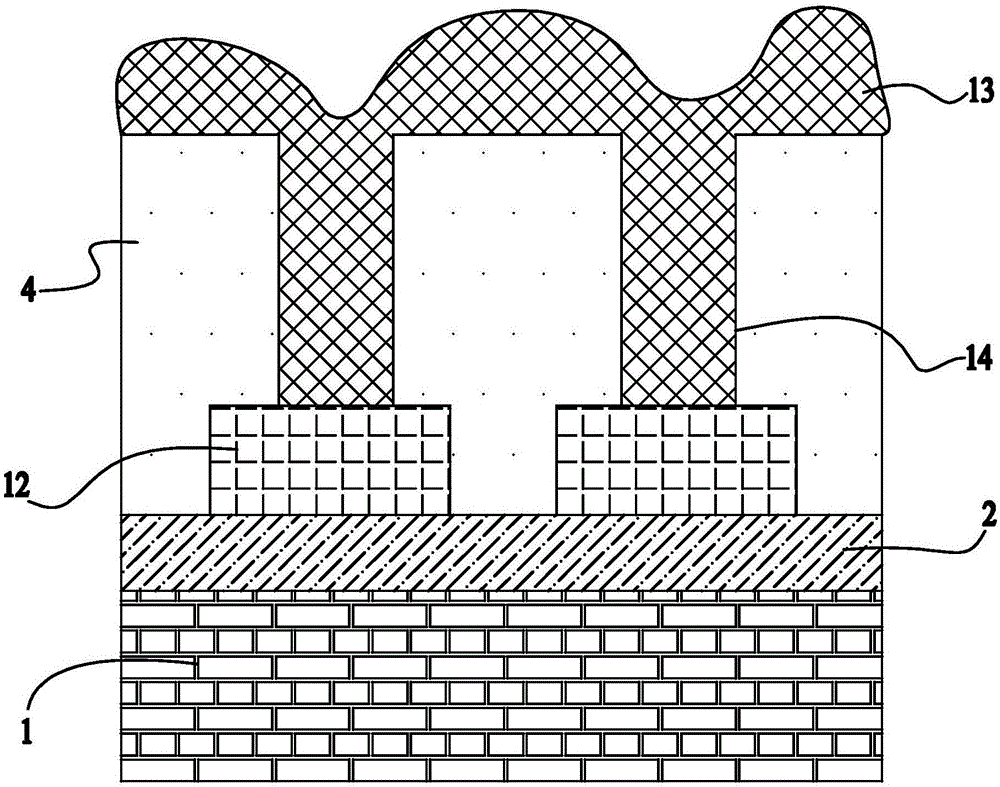

[0046] Such as Figure 12 As shown: In order to improve the integration level and improve the reliability of the antifuse, the present invention includes a substrate 1 and a device layer 2 located on the substrate 1; a fuse seal is pressed on the device layer 2 20. A lower fuse electrode is provided inside the fuse enclosure 20, and an upper fuse electrode 21 is provided outside the fuse enclosure 20, and the upper fuse electrode 21 is located directly above the lower fuse electrode ; An antifuse dielectric structure and an antifuse bottom barrier 17 are provided between the fuse upper electrode 21 and the fuse bottom electrode, and the antifuse bottom barrier 17 wraps the fuse bottom electrode in the fuse seal The top end of the anti-fuse medium structure is supported on the anti-fuse bottom barrier 17, and the upper fuse electrode 21 is supported on the anti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More