High-speed clock data recovery circuit of novel structure

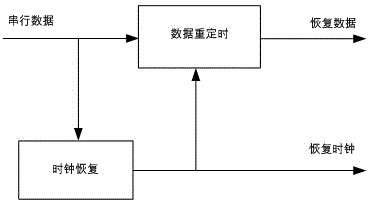

A high-speed clock, new structure technology, applied in the direction of electrical components, power automatic control, etc., can solve the problems of large area consumption, difficult design of linear phase detectors, etc., to save area and power consumption, solve the core voltage reduction, and improve the The effect of process portability and flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

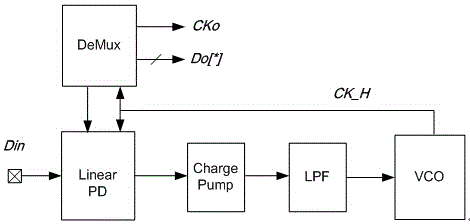

Method used

Image

Examples

Embodiment Construction

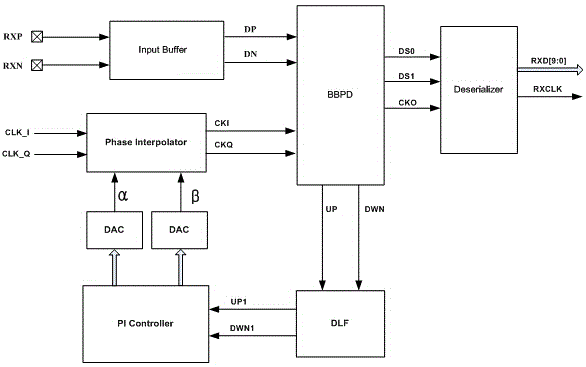

[0021] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

[0022] Such as image 3 As shown, after the high-speed serial data is shaped by the input data buffer, it enters the high-speed phase detector. The high-speed clocks CKI and CKQ with a difference of 90 degrees sample the serial data on both edges. The phase relationship between the high-speed clock and the serial data is obtained by XOR processing. The UP and DWN control signals output by the phase detector enter the digital loop filter for filtering processing, and the processed UP1 and DWN1 drive the phase interpolation controller to generate corresponding control information to drive the phase interpolator, and the high-speed clock output by the phase interpolator enters the detector phase device, thereby forming a negative feedback closed-loop system, and finally the phase relationship between the high-speed clock and data is locked at ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com