Multistage unit film transistor memory and preparation method thereof

A thin film transistor and memory technology, which is applied in the field of multi-level unit thin film transistor memory and its preparation, can solve the problems of increased device manufacturing cost and increased device preparation process complexity, and can reduce thermal budget and prevent physical properties and chemical composition from occurring. The effect of changing and reducing the loss of electric charge

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

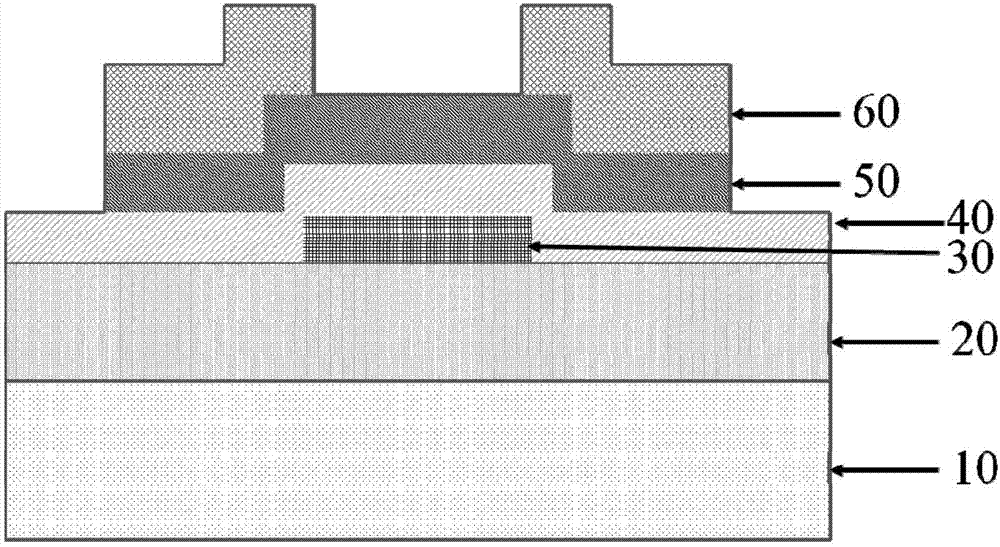

[0040] The present invention also provides a method for preparing the above-mentioned multi-level cell thin film transistor memory, which includes the following steps:

[0041] Step 1, preparing the gate electrode 10;

[0042] Step 2, growing a charge blocking layer 20 on the gate electrode 10 obtained in step 1 by atomic layer deposition, the thickness of the charge blocking layer 20 is 30-60nm, and the deposition temperature is 150-350°C;

[0043]Step 3, growing a charge-trapping layer 30 on the charge-blocking layer 20 obtained in step 2 by atomic deposition or magnetron sputtering deposition, and the thickness of the charge-trapping layer 30 is 10-40 nm;

[0044] Step 4. Spin-coat a layer of positive photoresist on the charge-trapping layer 30 obtained in step 3, then perform photolithography to define the area of the charge-trapping layer 30, and then use a wet etching process to etch the defined area The portion outside the region of the charge trapping layer 30;

[...

Embodiment 1

[0051] In this embodiment, a ZnO thin film is used as the charge trapping layer 30, and the specific preparation process is as follows:

[0052] Step 1, using a P-type monocrystalline silicon wafer with a resistivity of 0.001-0.005Ω·cm as a substrate, and using a standard RCA cleaning process to clean the substrate to form a gate electrode 10;

[0053] Step 2, growing a layer of Al on the gate electrode 10 by ALD method 2 o 3 The film is used as the charge blocking layer 20; the deposition temperature is 150-350°C, preferably 300°C; the film thickness is 30-60nm, preferably 35nm;

[0054] Step 3, growing a layer of ZnO film on the charge blocking layer 20 by ALD method or PVD method as the charge trapping layer 30; the deposition temperature is 150-350°C, preferably 200°C; the film thickness is 10-40nm, preferably 20nm;

[0055] Step 4, spin-coat a layer of positive photoresist on the charge-trapping layer 30, then perform exposure and development to define the region of the...

Embodiment 2

[0063] In this embodiment, an IGZO thin film is used as the charge trapping layer 30, and the specific preparation process is as follows:

[0064] Step 1, using a P-type monocrystalline silicon wafer with a resistivity of 0.001-0.005Ω·cm as a substrate, and using a standard RCA cleaning process to clean the substrate to form a gate electrode 10;

[0065] Step 2, grow a layer of Al on the gate electrode 10 by ALD method 2 o 3 The film is used as the charge blocking layer 20; the deposition temperature is 150-350°C, preferably 300°C; the film thickness is 30-60nm, preferably 35nm;

[0066] Step 3, grow a layer of IGZO film by PVD method on the charge blocking layer 20 as the charge trapping layer 30; the atomic ratio of the IGZO target is In:Ga:Zn:O=1:1:1:4, and the sputtering power is 110W, the working pressure is 0.88Pa, the Ar and O 2 The flow rates are 50sccm and 0sccm respectively; the thickness of the IGZO film is 10-40nm, preferably 20nm;

[0067] Step 4, spin-coat a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More