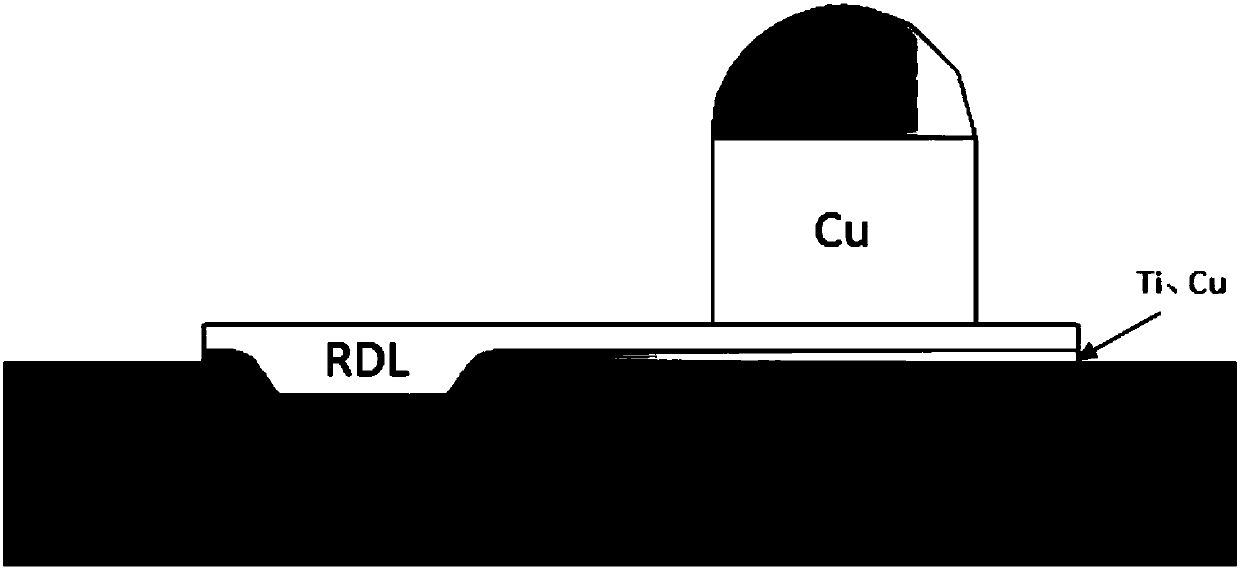

1P2M CMOS packaging method

An encapsulation method and passivation layer technology, which are applied to electrical components, electrical solid-state devices, circuits, etc., can solve the problems of long operation time and high material cost, and achieve the effect of saving operation time, material cost and good application prospect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

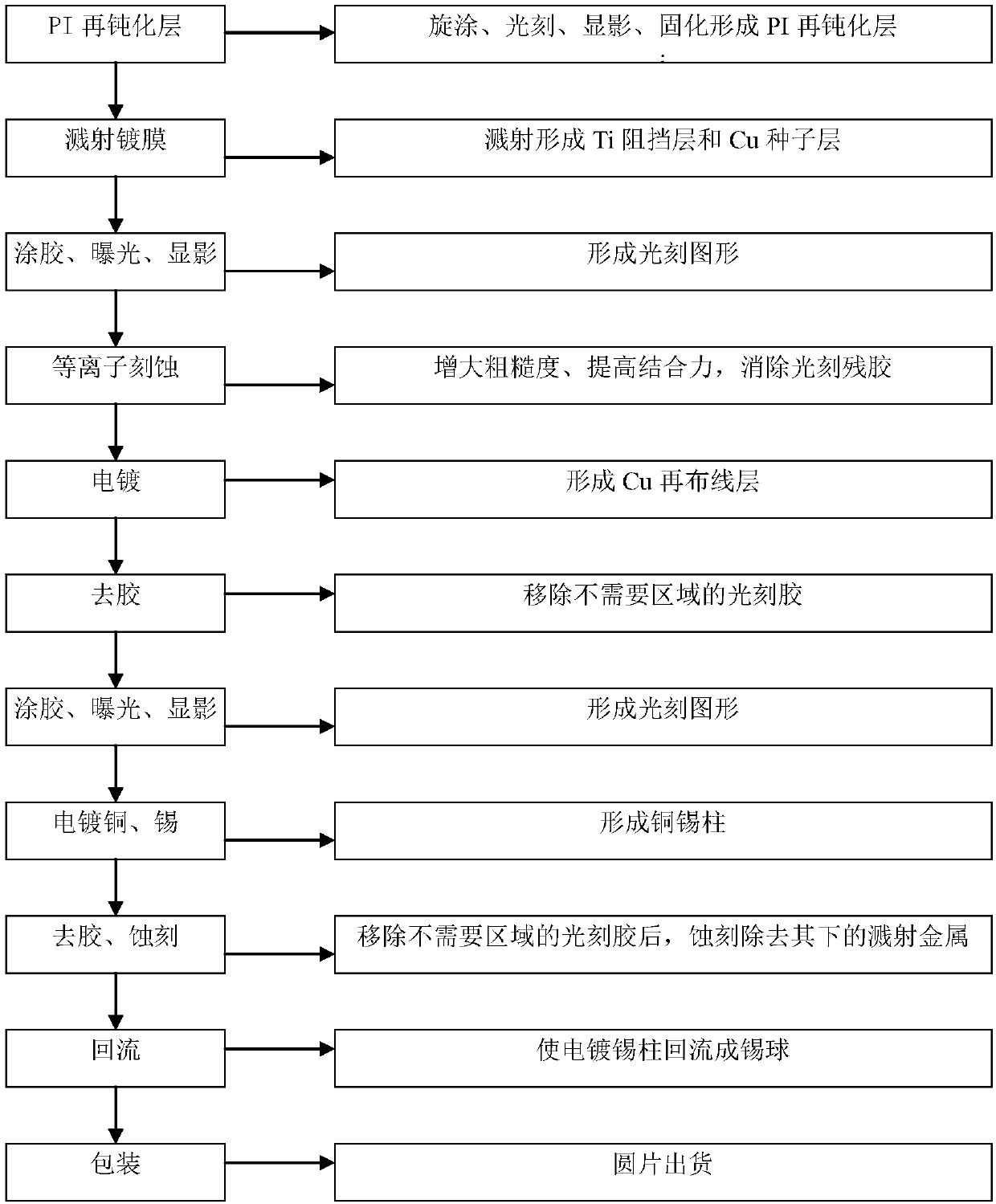

[0024] 1) Multi-layer polyimide (PI) passivation layer coating process

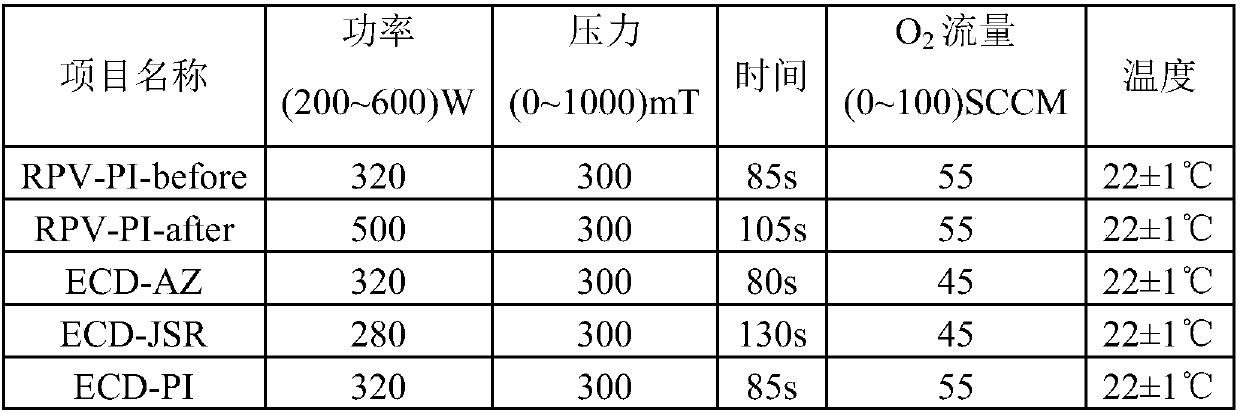

[0025] Polyimide (PI) photoresist has outstanding heat resistance, excellent mechanical properties, insulation and corrosion resistance. First, the automatic coating machine quantitatively coats 5ml of PI glue on the surface of the wafer, and finally forms a layer of 5um polyimide re-passivation layer on the surface of the wafer through spin coating, pre-baking, photolithography, development and curing processes , play the role of insulation, corrosion resistance, stress buffer and planarization. Among them, spin coating is divided into uniform glue (200±20rpm, 7±1s), spin glue (2450±100rpm, 30±3s), BSR (1000±50rpm, 15±1s), spin dry (1000±50rpm, 10±1s) ), side throwing (3000±50rpm, 1±0.1s) 5 processes, stepper exposure is carried out under the exposure energy of 300mj and the spacing of 4um after the coating is completed, and the developer is KS5400 (Shanghai Feikai Optoelectronic Materials Co., Ltd.) D...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com