Capacitor array structure and manufacture method thereof

A technology of array structure and manufacturing method, which is applied in the direction of capacitors, electric solid devices, circuits, etc., can solve the problems of affecting the performance, the conductivity of the capacitor medium layer increases the leakage current, and the presence of bubbles, so as to reduce the impact, reduce the formation process temperature, Effect of increasing movement speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

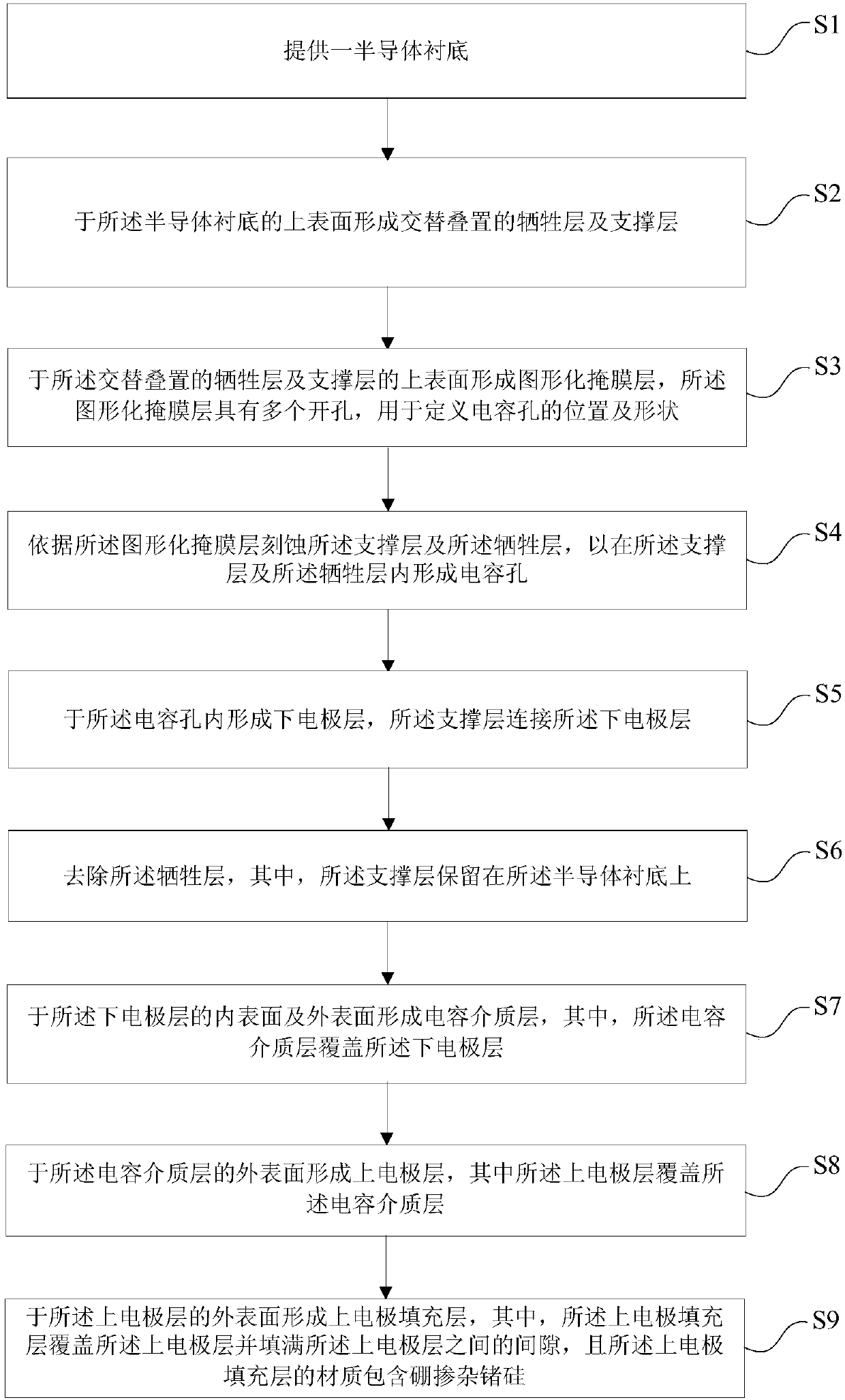

[0080] See figure 1 This embodiment provides a method for manufacturing a capacitor array structure. The method for manufacturing the capacitor array structure includes the following steps:

[0081] 1) Provide a semiconductor substrate;

[0082] 2) Forming alternately stacked sacrificial layers and supporting layers on the upper surface of the semiconductor substrate;

[0083] 3) forming a patterned mask layer on the upper surface of the alternately stacked sacrificial layer and support layer, the patterned mask layer having a plurality of openings for defining the position and shape of the capacitor hole;

[0084] 4) Etching the support layer and the sacrificial layer according to the patterned mask layer to form capacitor holes in the support layer and the sacrificial layer;

[0085] 5) forming a lower electrode layer in the capacitor hole, and the support layer is connected to the lower electrode layer;

[0086] 6) removing the sacrificial layer, wherein the supporting layer remains o...

Embodiment 2

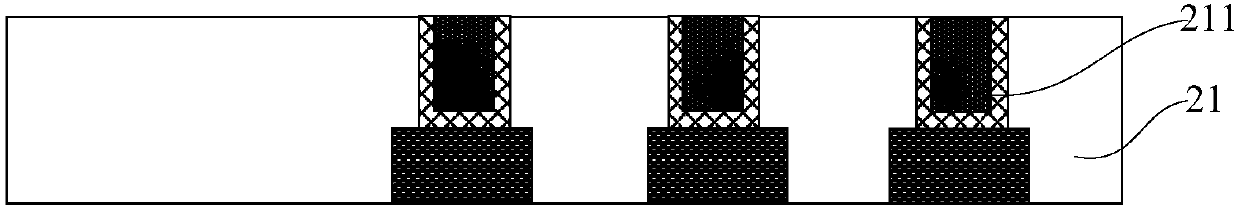

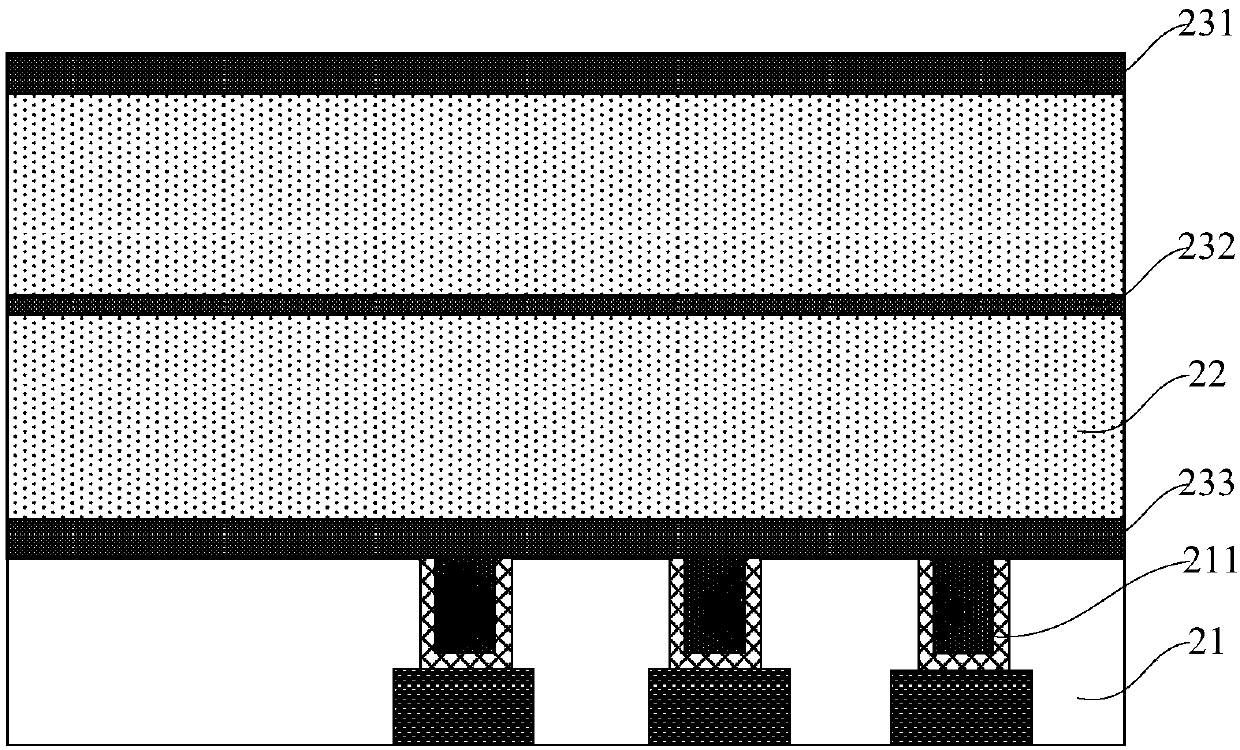

[0136] Please continue to refer to Example 1 Figure 13 This embodiment also provides a capacitor array structure which is manufactured by the manufacturing method described in the first embodiment, the capacitor array structure is disposed on the semiconductor substrate 21, and the semiconductor substrate 21 A plurality of pads 211 in a memory array structure are formed thereon. The capacitor array structure includes a lower electrode layer 26, the lower electrode layer 26 is bonded to the pad 211, and the cross-sectional shape of the lower electrode layer 26 U-shaped; the capacitor dielectric layer 27, the capacitor dielectric layer 27 covers the inner and outer surfaces of the lower electrode layer 26; the upper electrode layer 28, the upper electrode layer 28 covers the capacitor dielectric layer 27 The outer surface; the upper electrode filling layer 29, the upper electrode filling layer 29 covers the outer surface of the upper electrode layer 28, and fills the gap between...

Embodiment 3

[0153] This embodiment also provides a semiconductor storage device structure. The semiconductor storage device structure includes the capacitor array structure described in the second embodiment. For the specific structure of the capacitor array structure, please refer to the second embodiment. Narrated.

[0154] As an example, the structure of the semiconductor memory device may be, but is not limited to, a dynamic random access memory (DRAM).

[0155] In summary, the capacitor array structure and the manufacturing method thereof of the present invention include the following steps: 1) providing a semiconductor substrate; 2) forming alternate stacks on the upper surface of the semiconductor substrate 3) A patterned mask layer is formed on the upper surface of the alternately stacked sacrificial layer and the support layer. The patterned mask layer has a plurality of openings for defining capacitor holes 4) etching the support layer and the sacrificial layer according to the patt...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More