Wafer warping elimination method and composite substrate

A composite substrate and wafer technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increasing device cost, high cost, increasing device process difficulty, etc., to reduce the probability of fragmentation or fragmentation, Easy to identify and locate, and the effect of eliminating warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] This implementation provides a method for eliminating wafer warpage, the method comprising the steps of:

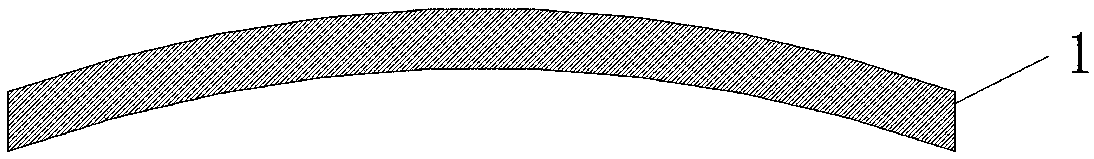

[0043] S1: Select a warped wafer 1;

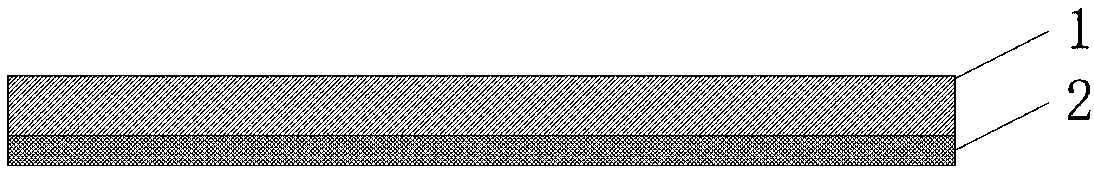

[0044] S2: Deposit a layer of stress compensation film 2 with internal stress on the back of the wafer 1, so that the internal stress of the stress compensation film 2 and the internal stress of the wafer 1 cancel each other out to obtain a flat composite substrate.

[0045] The above-mentioned wafer 1 is a silicon carbide-based silicon carbide wafer or a silicon-based gallium nitride wafer.

[0046] The material of the stress compensation film 2 is preferably silicon oxide, silicon nitride or metal.

[0047] The internal stress of the above-mentioned stress compensation film 2 is compressive stress, no stress or tensile stress. Those skilled in the art can adjust the type of internal stress (compressive stress, no stress or tensile stress) of the deposited stress compensation film 2 by adjusting the process parameters of the...

Embodiment 2

[0051] This implementation provides a method for eliminating wafer warpage, the method comprising the steps of:

[0052] S1: Select a warped wafer 1;

[0053] S2: Deposit a layer of stress compensation film 2 with internal stress on the back of the wafer 1, so that the internal stress of the stress compensation film 2 and the internal stress of the wafer 1 cancel each other out to obtain a flat composite substrate.

[0054] The above-mentioned wafer 1 is a silicon carbide-based silicon carbide wafer or a silicon-based gallium nitride wafer.

[0055]The material of the stress compensation film 2 is preferably silicon oxide, silicon nitride or metal.

[0056] The internal stress of the above-mentioned stress compensation film 2 is compressive stress, no stress or tensile stress. Those skilled in the art can adjust the type of internal stress (compressive stress, tensile stress or no stress) of the deposited stress compensation film 2 by adjusting the process parameters of the ...

Embodiment 3

[0060] This implementation provides a method for eliminating wafer warpage, the method comprising the steps of:

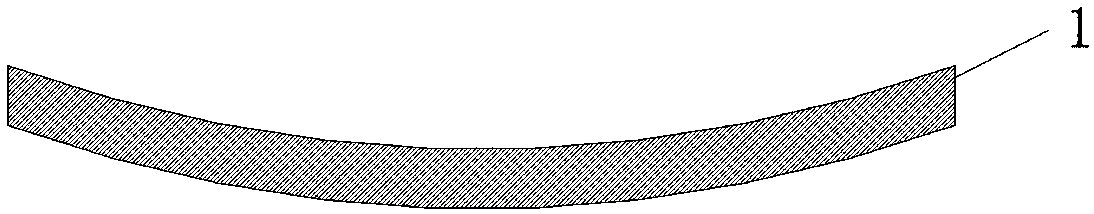

[0061] S1: Select a warped wafer 1;

[0062] S2: Depositing a layer of stress compensation film 2 with internal stress on the back of the wafer 1, so that the internal stress of the stress compensation film 2 and the internal stress of the wafer 1 cancel each other out to obtain a flat composite substrate;

[0063] S3: Depositing an auxiliary film 3 with no internal stress on the back of the above stress compensation film 2 .

[0064] The above-mentioned wafer 1 is a silicon carbide-based silicon carbide wafer.

[0065] The material of the stress compensation film 2 is preferably silicon oxide, silicon nitride or metal.

[0066] The internal stress of the above-mentioned stress compensation film 2 is compressive stress, no stress or tensile stress. Those skilled in the art can adjust the type of internal stress (compressive stress, zero stress or tensile stress)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More