Three-dimensional photoelectric integrated filter realized based on CMOS post-process and preparation method thereof

A photoelectric integration and filter technology, which is applied in the direction of electrical solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of center wavelength drift, very strict working temperature requirements, and sensitivity to temperature changes, and achieve the effect of improving bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

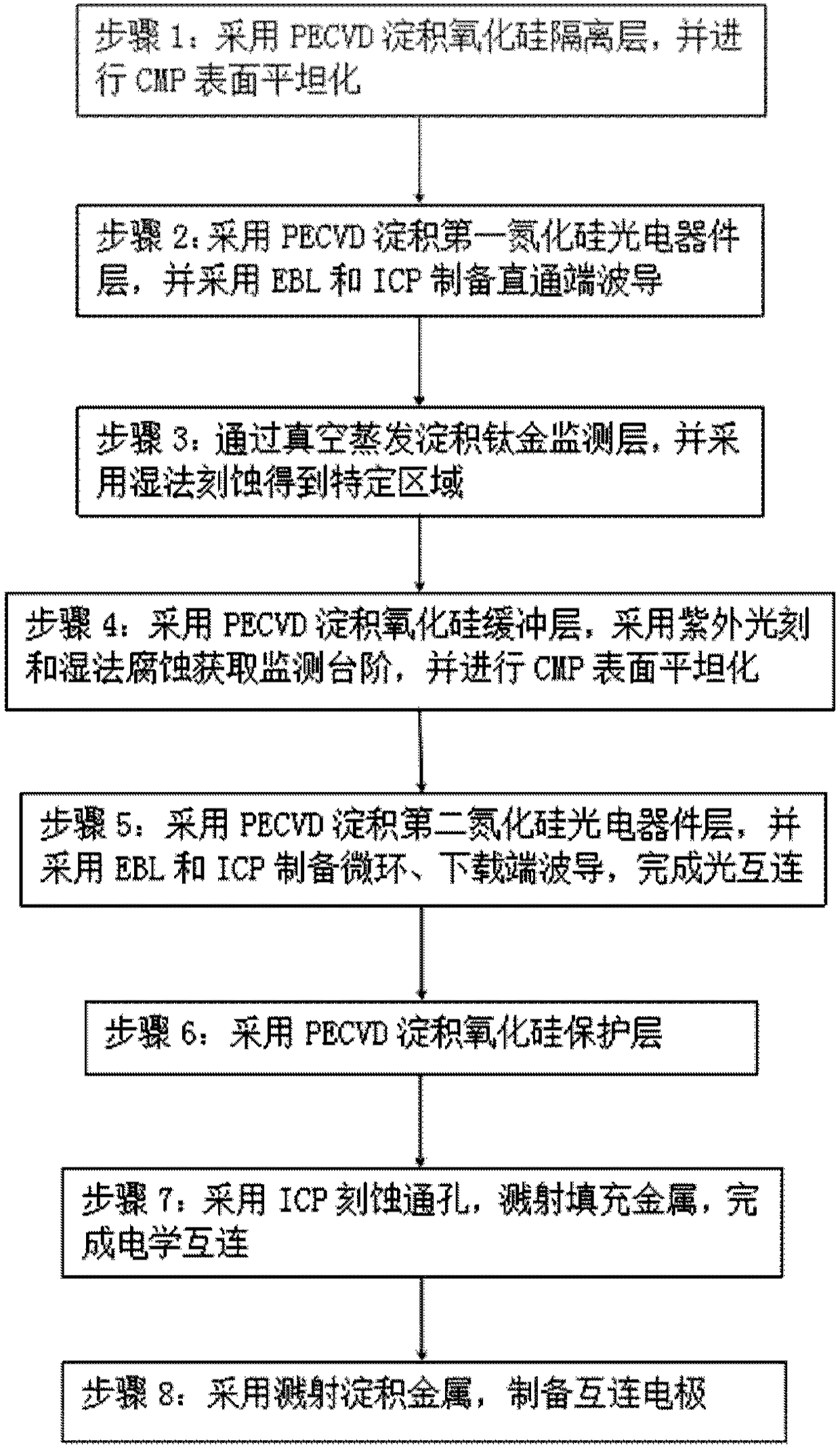

[0041] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0042] The present invention proposes a three-dimensional photoelectric integrated filter based on post-CMOS technology. All process temperatures are controlled below 400°C to avoid impact on the CMOS integrated circuit, realize single-chip integration of photoelectric devices and CMOS integrated circuits, and simultaneously realize three-dimensional optical Interconnection solves the bottleneck problem of electrical interconnection.

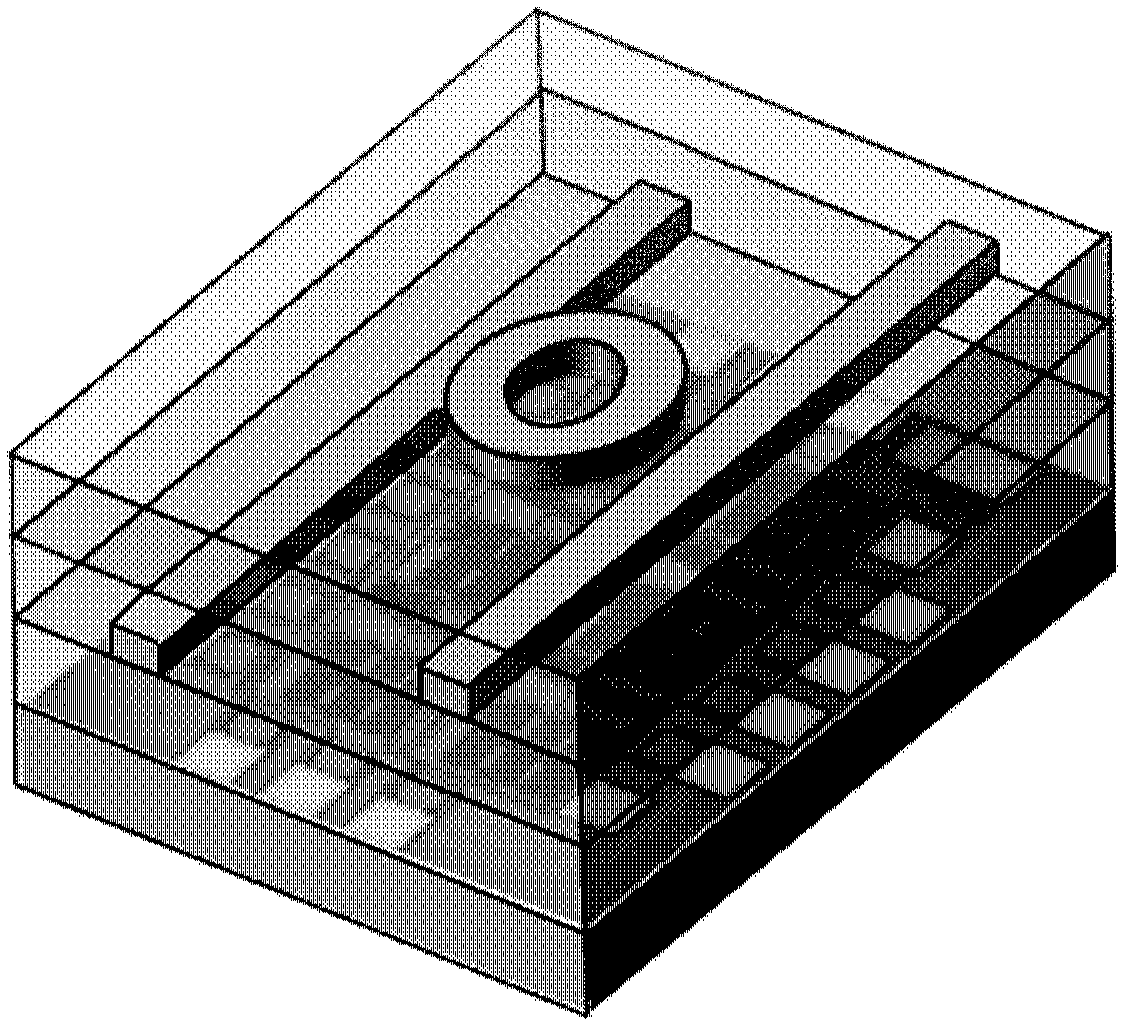

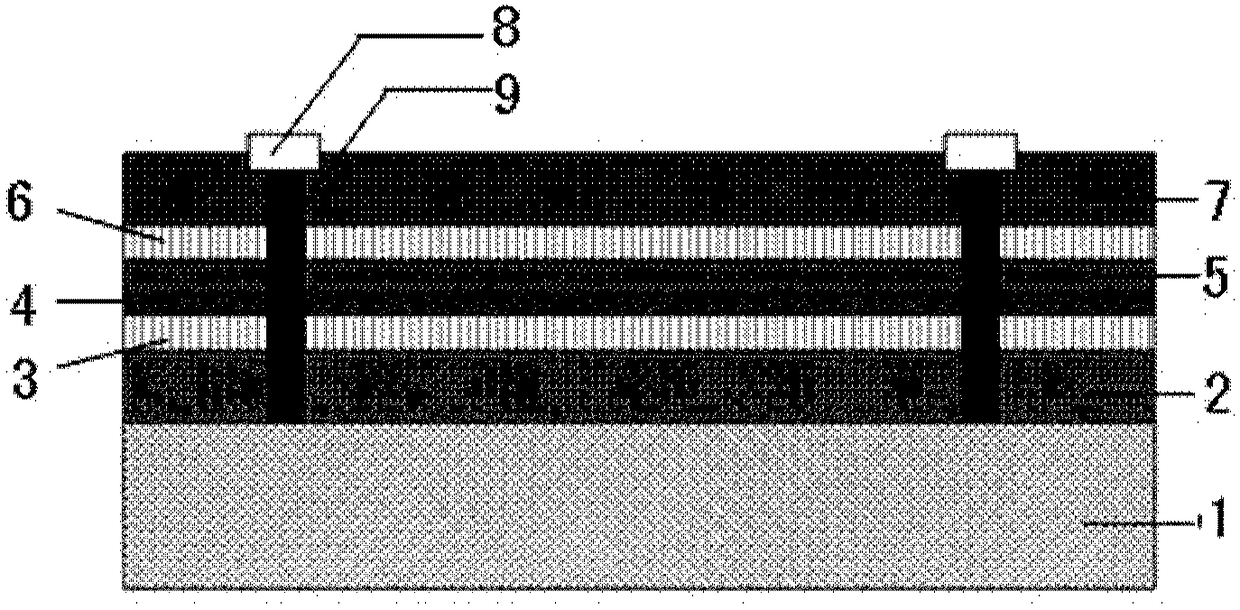

[0043] refer to figure 1 and figure 2 , the present invention is based on the three-dimensional optoelectronic integrated filter realized by the post-CMOS process, including the silicon oxide isolation layer 2, the first silicon nitride optoelectronic device layer 3, and the titanium gold...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More