A semiconductor memory aging test system and method

An aging test and memory technology, applied in static memory, instruments, etc., can solve problems such as no test process recording and management analysis, no test process and result management analysis, no mention of high and low temperature aging test solutions, etc. Test signal quality, improve scalability, reduce temperature shock effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

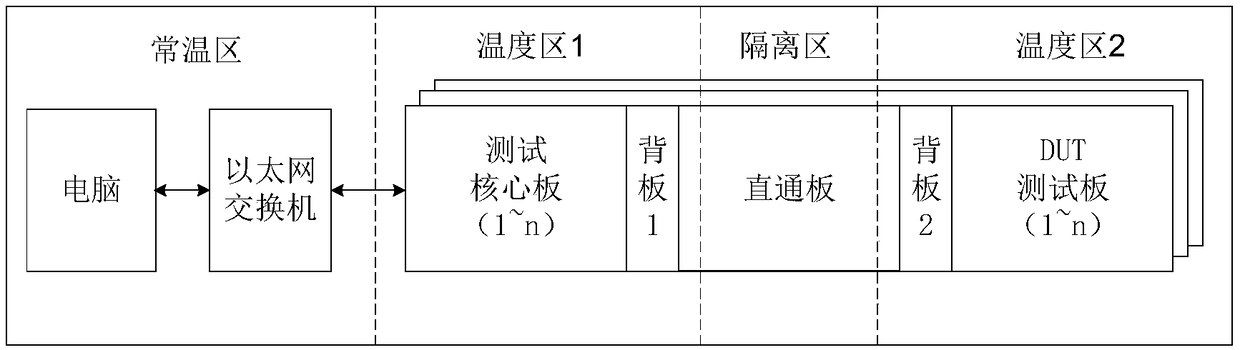

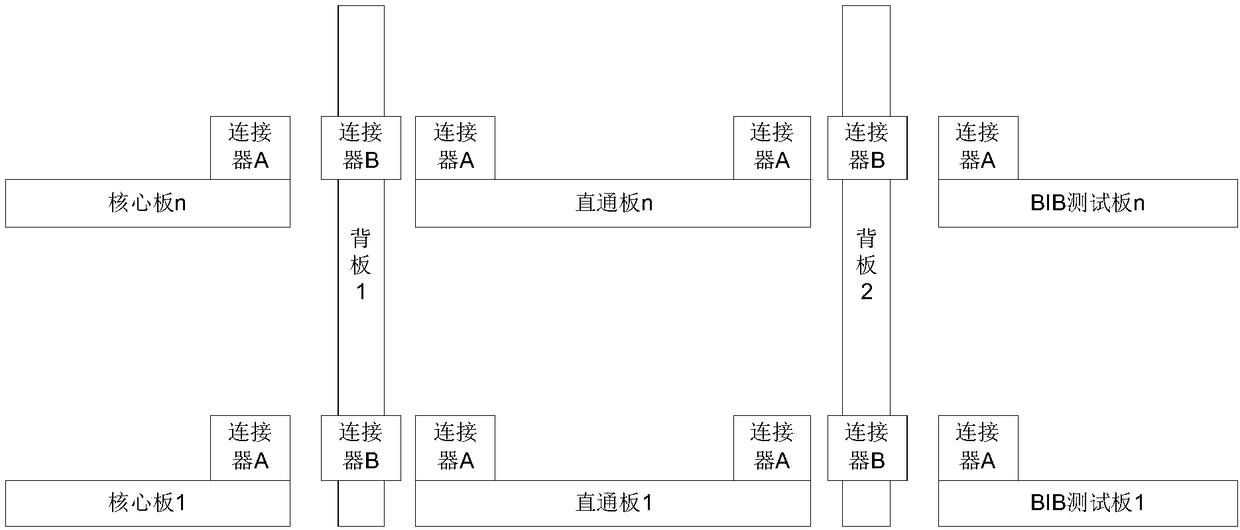

[0054] refer to Figure 1 to Figure 5 , to describe an embodiment of the semiconductor memory burn-in test system provided by the present invention.

[0055] The semiconductor memory burn-in test system provided by the embodiment includes a host computer, a switch, a test core board, a first backplane, a test board, and a second backplane;

[0056] The host computer is used to run the test sof...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More