A high early voltage bipolar device and its manufacturing method

A technology of bipolar devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., and can solve the problems of increased output fluctuations of reference sources, low threshold voltage of parasitic PMOS, and low impurity concentration on the surface of epitaxial layers, etc. , to achieve the effect of increasing the Early voltage, increasing the threshold voltage, and reducing the Early effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

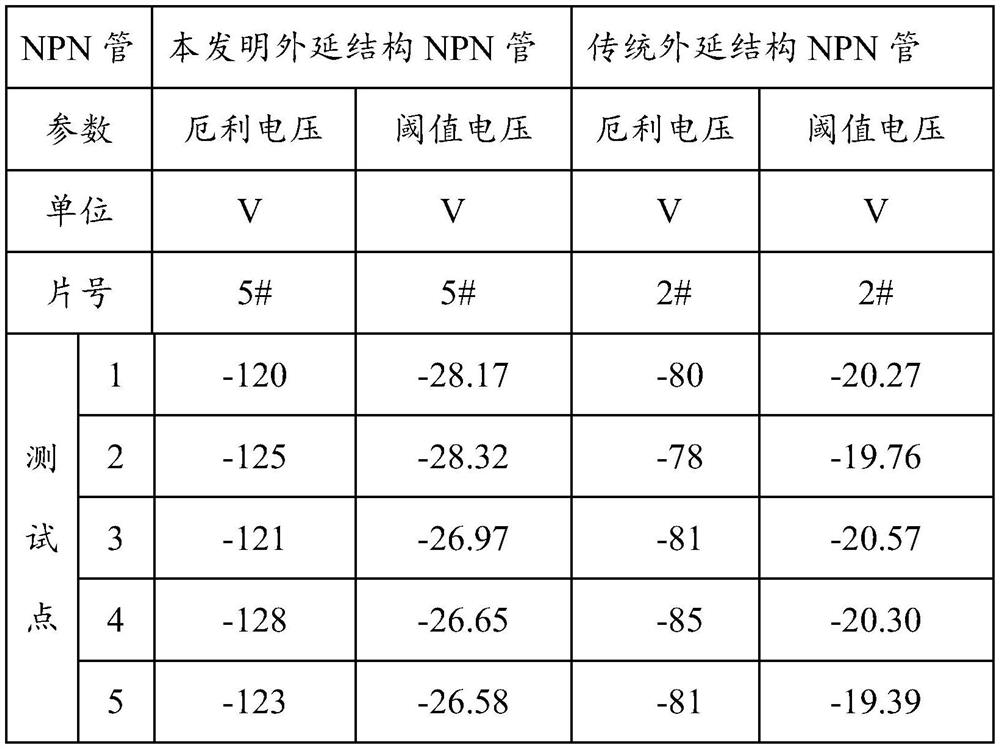

[0069] Adopt novel vertical NPN transistor of the present invention, apply OP77 bipolar integrated circuit, the double-layer epitaxy result that adopts is as follows:

[0070] 1) The process design of the first epitaxial layer is: the thickness is 15 μm, and the resistivity is 6.0Ω·cm;

[0071] 2) The process design of the second epitaxial layer is as follows: the thickness is 2 μm, and the resistivity is 3.2 Ω·cm.

[0072] The effect of using this structure:

[0073] The voltage gain of the product is increased from 130db to 135db, which meets the requirements of use.

Embodiment 2

[0075] For 50V high-precision high-voltage bipolar integrated circuits, the traditional epitaxial process conditions are: thickness 13 μm, resistivity 4Ω cm; using double-layer epitaxial process, the first layer epitaxial process design is: thickness 15 μm, 6Ω cm; second layer The epitaxial process design is: thickness 2μm, resistivity 3.2Ω cm;

[0076] The layout structure of the NPN tube is: the base area is 26 μm × 26 μm, and the emission area is 10 μm × 10 μm.

[0077] The dielectric structure under the parasitic PMOS metal is: 600nm SiO 2 and 100nm Si 3 N 4 .

[0078] Early voltage test conditions: Ic 0.5mA, see Table 1 for comparative test results.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More