Method for manufacturing a low-temperature polysilicon display panel

A technology of low-temperature polysilicon and a manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as pollution, avoid lattice defects, improve lattice arrangement structure, and improve yield and quality. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

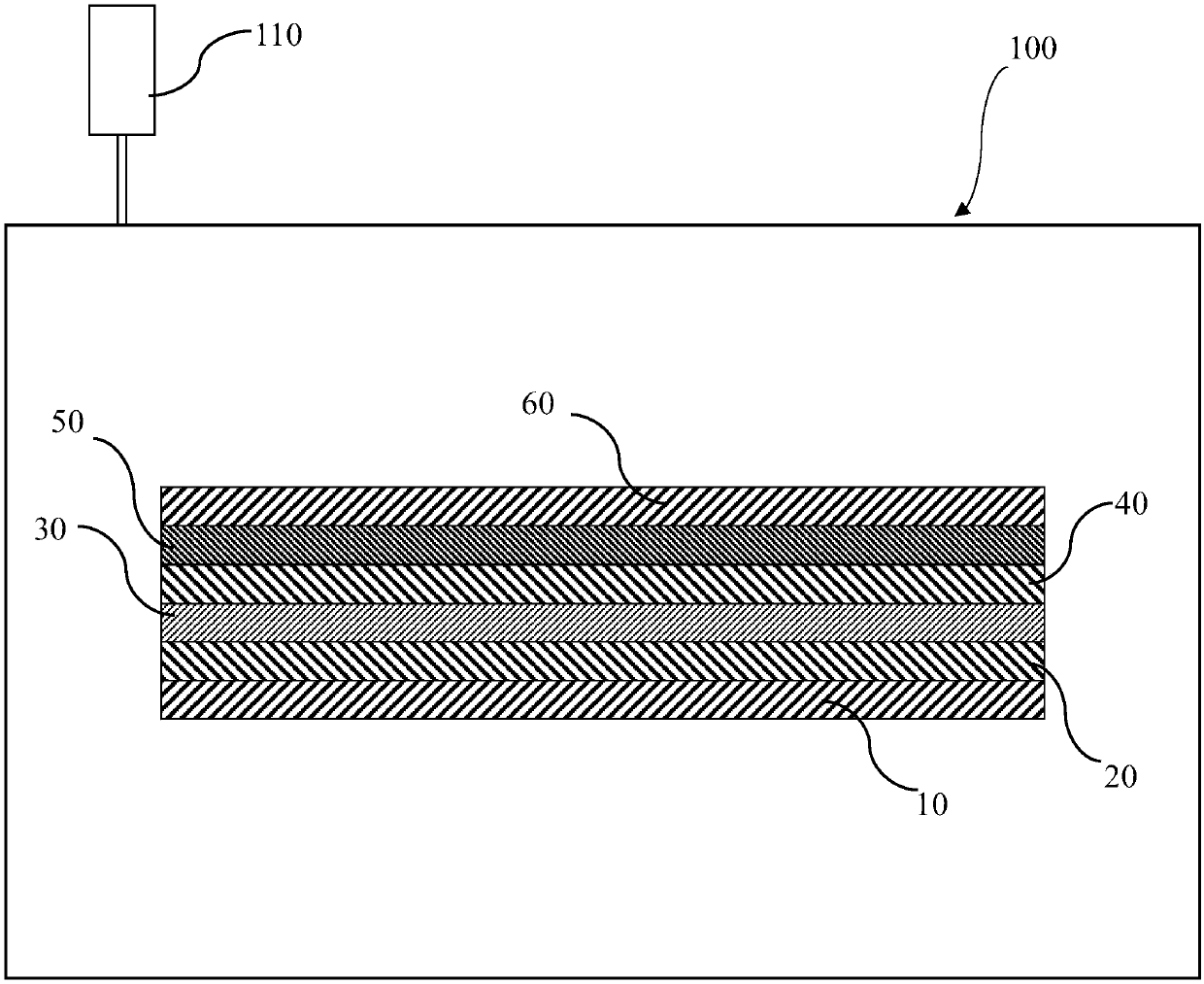

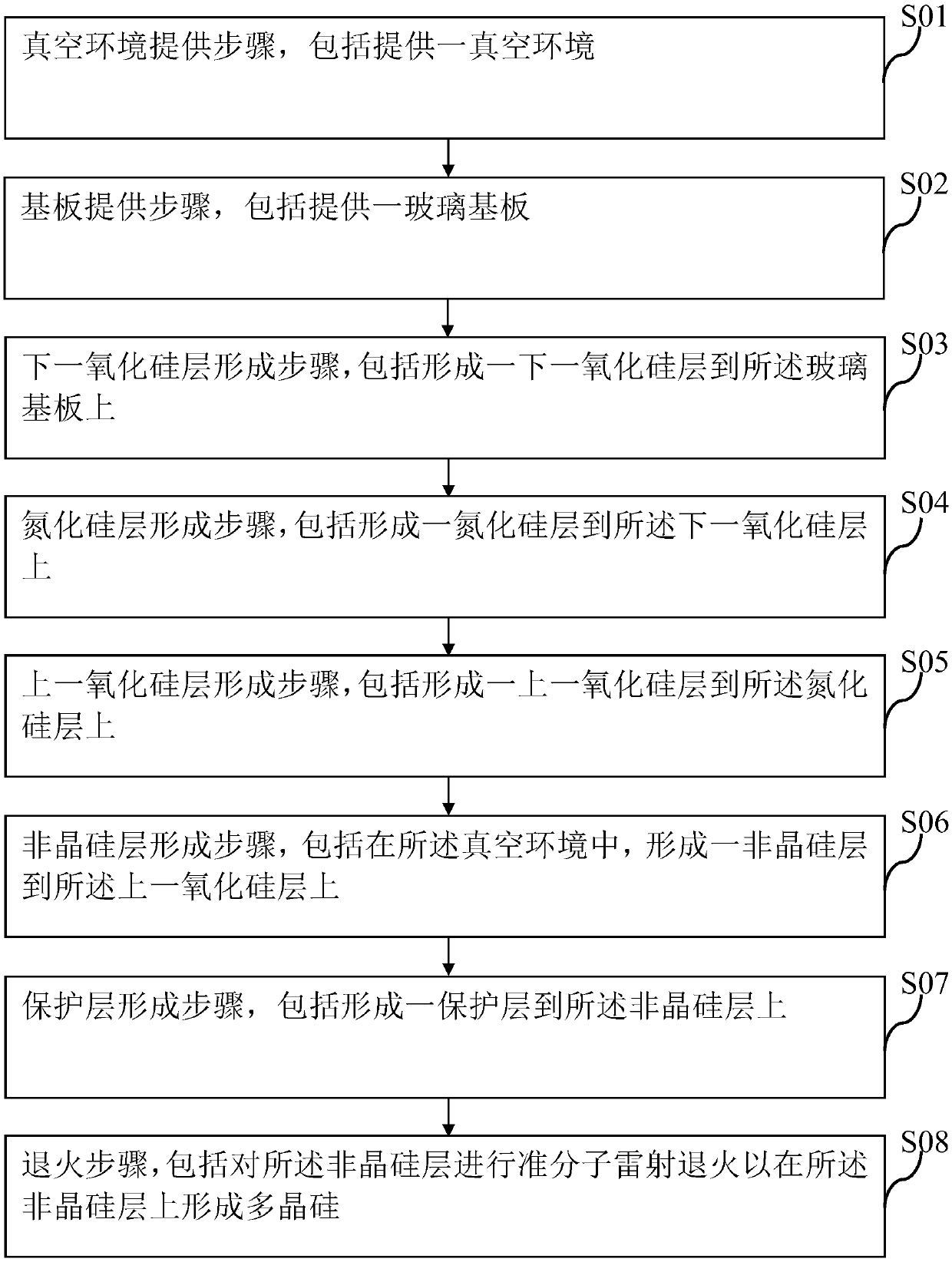

[0029] Please refer to figure 1 and figure 2 , The method for manufacturing a low-temperature polysilicon display panel of the present invention includes: a vacuum environment providing step S01, a substrate providing step S02, a next silicon oxide layer forming step S03, a silicon nitride layer forming step S04, a silicon nitride layer forming step S04, the previous A silicon oxide layer forming step S05, an amorphous silicon layer forming step S06, a protective layer forming step S07, and an annealing step S08.

[0030] The vacuum environment providing step S01 includes providing a vacuum environment 100 . In an embodiment of the present invention, the vacuum environment 100 is a vacuum chamber. The vacuum chamber is connected with a vacuum pump 110, and the vacuum pump 110 is used to evacuate the vacuum chamber. The vacuum pump 110 can evacuate the vacuum chamber in the whole process to maintain the vacuum degree in the vacuum chamber. Alternatively, the vacuum pump 11...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More