Method for manufacturing magnetic random access memory cell array and peripheral circuit connection line

A random access memory and cell array technology, applied in the manufacture/processing of electromagnetic devices, circuits, parts of electromagnetic equipment, etc., can solve problems such as time-dependent dielectric breakdown, damage diffusion barrier, damage, etc., to reduce complexity And the effect of production cost, electrical performance and yield improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment example 1

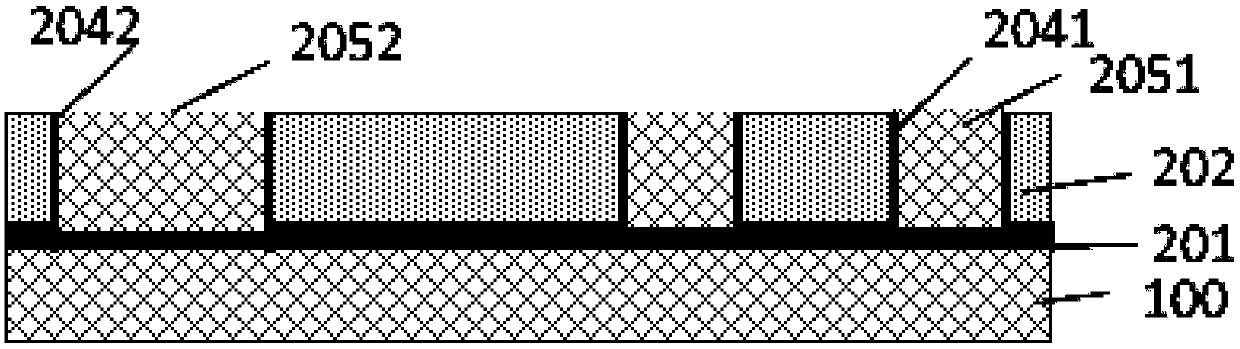

[0062] Implementation case 1: two single damascene (SD, Single Damascene) processes, the steps are as follows:

[0063] Step 4.1.1: On the magnetic tunnel junction dielectric layer 304, deposit the top electrode through hole dielectric 401 and fill the dummy magnetic tunnel junction (Dummy-MTJ) opening 306, and finally, use the planarization process to grind the top electrode through hole ( TEV) dielectric 401, as shown in Figure 4(a); the top electrode via (TEV) dielectric 401 is SiO 2 , SiON or low-k and other materials, the thickness of which is 120nm ~ 400nm.

[0064] Step 4.1.2: Graphically define and form a top electrode through hole (TEV) 4021 and a top electrode through hole 4022 by an etching process. In the logic area, it is connected to the bottom electrode to contact the metal layer 301, and the process parameters are strictly controlled to keep a sufficient distance between the top electrode through hole (TEV) 4022 and the side wall of the dummy magnetic tunnel j...

Embodiment example 2

[0068] Implementation Case 2: Single Dual Damascene (DD, Dual Damascene) process, such as Figure 5 shown; the steps are as follows:

[0069] Step 4.2.1: On the magnetic tunnel junction dielectric layer 304, deposit the top electrode through hole dielectric 401 and fill the dummy magnetic tunnel junction (Dummy-MTJ) opening 306, and then use the planarization process to grind the top electrode through hole ( TEV) dielectric 401; top electrode via (TEV) dielectric 401 is SiO 2 , SiON or low-k and other materials, the thickness of which is 120nm ~ 400nm; finally, deposit metal wiring (M x+1 ) The thickness of the dielectric 406 is 50nm-300nm, and its material is SiO 2 , SiON or low-k, etc., usually before deposition, an etch barrier layer 405 with a thickness of tens of nanometers is deposited, and its material is SiN, SiC or SiCN, etc.;

[0070] Step 4.2.2: Graphically define and use an etching process to form the top electrode through hole (TEV) and the metal wiring groove ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More