Field-effect transistor manufacturing method and field-effect transistor

A manufacturing method and field effect tube technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high cost and complicated process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

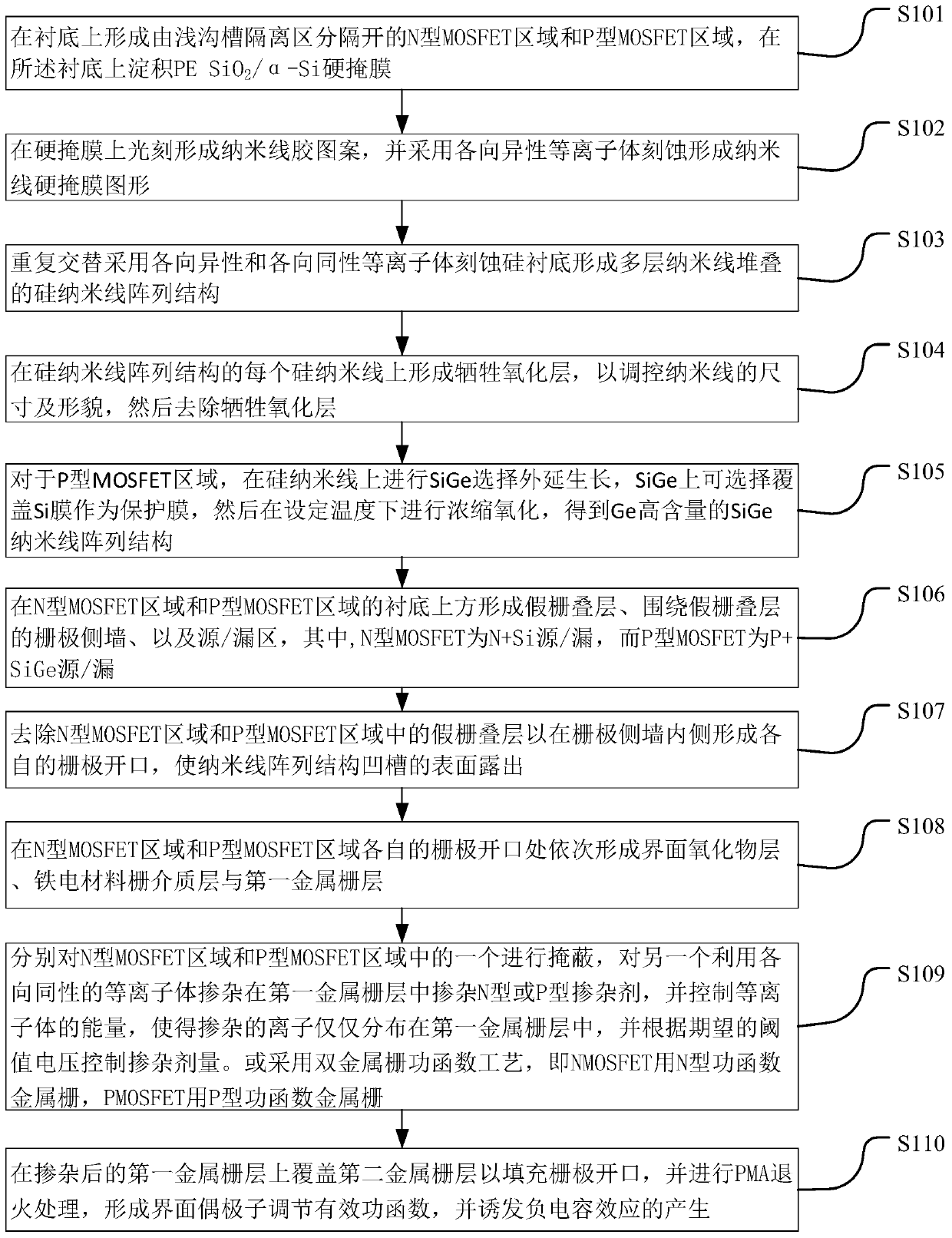

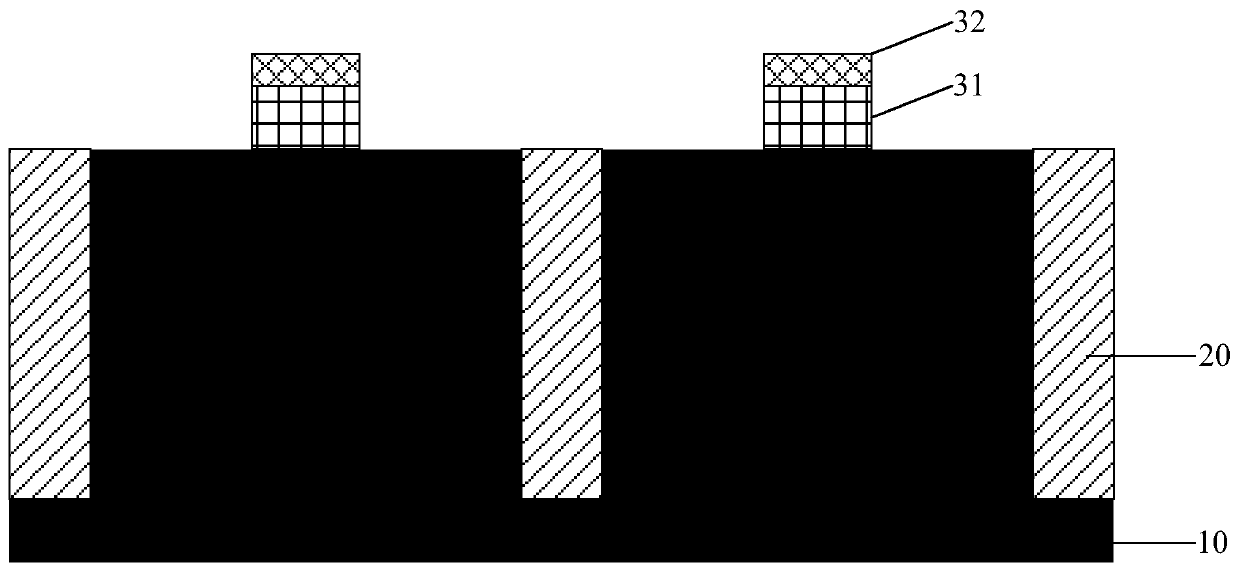

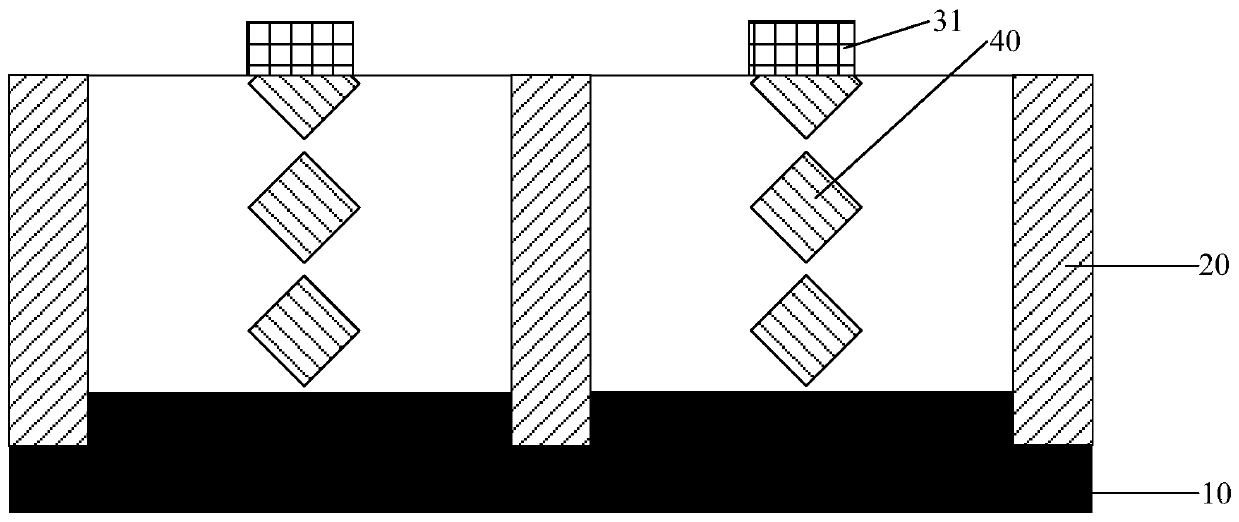

[0080]The present disclosure is to provide a ferroelectric material negative capacitance nanowire array ring-gate complementary field effect transistor structure and a manufacturing method thereof. The ferroelectric material negative capacitance nanowire array ring-gate CMOSFET structure has an N-type MOSFET region and a P-type MOSFET at the same time. area, not only retains the good electron mobility of the Si nanowire gate NMOSFET, but also improves the hole mobility of the SiGe nanowire gate PMOSFET. Moreover, because the nanowire ring-gate structure greatly improves the gate control ability, it suppresses the short-channel effect extremely well. In particular, the nanowire array ring-gate CMOSFET structure of the present disclosure integrates the ferroelectric negative capacitance effect, which effectively increases the surface potential of the device channel, making it greater than the external gate voltage, which realizes the voltage amplification effect and breaks throug...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More