A process for manufacturing a 0.15-micron T-shaped grid

A production method and process technology, which is applied in the field of 0.15 micron T-shaped gate process, can solve the problems of long production cycle and low precision, and achieve the effects of saving time, improving work efficiency, and not affecting the isolation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

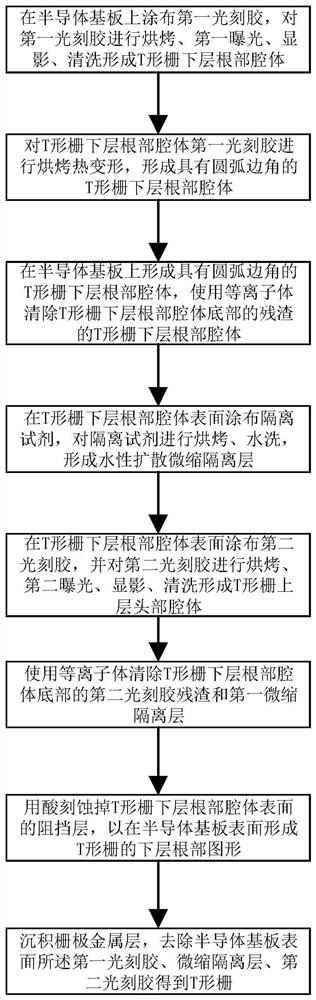

[0047] like figure 1 Shown, in embodiment 1, a kind of process manufacturing method of 0.15 micron T-shaped gate, the method specifically comprises the following steps:

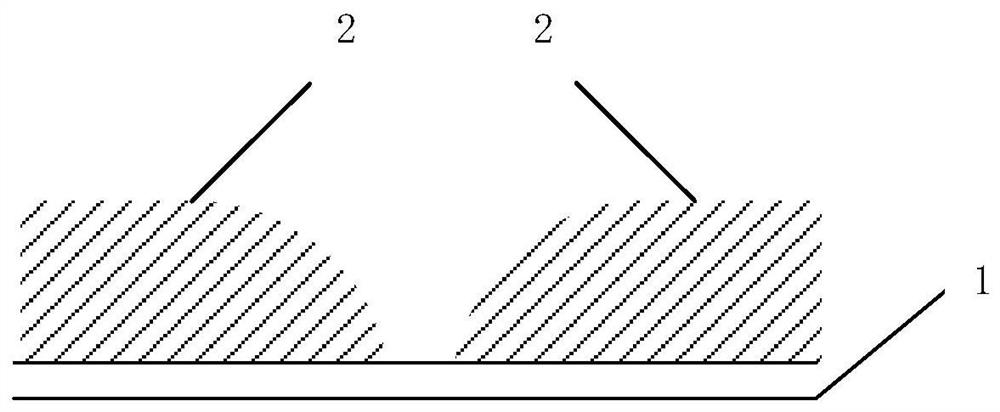

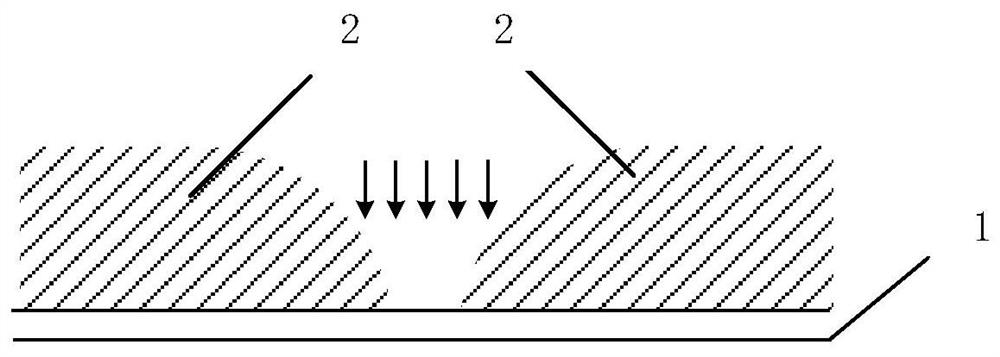

[0048] S01: Form a T-shaped grid lower root cavity with arc corners on the semiconductor substrate 1, and use plasma to remove the residue at the bottom of the T-shaped grid lower root cavity; specifically, as figure 2As shown, the characteristic size of the lower root cavity of the T-shaped gate with rounded corners is smaller than the target characteristic size of 0.15 μm, and the characteristic size of the lower root cavity of the T-shaped gate is that the lower root cavity on both sides of the T-shaped gate is in contact with the semiconductor substrate. The relative distance of the position; such as image 3 As shown, the plasma used is O2 plasma, and the flow rate of O2 plasma is controlled at 1-4Torr, and the power is controlled at 10-170W, which can clean the residue at the bottom of the root cavity...

Embodiment 2

[0056] This embodiment has the same inventive idea as Embodiment 1, and this embodiment is a further optimization based on Embodiment 1. Specifically, this embodiment provides a process for manufacturing a 0.15-micron T-shaped grid. The method is specific Include the following steps:

[0057] S11: Form a T-shaped grid lower root cavity with rounded corners on the semiconductor substrate 1, and use plasma to remove residues at the bottom of the T-shaped grid lower root cavity; wherein, the T-shaped lower root cavity with rounded corners The characteristic size of the cavity is smaller than the target characteristic size of 0.15 μm, and the characteristic size of the lower root cavity of the T-shaped grid is the relative distance between the lower root cavity on both sides of the T-shaped grid and the contact position of the semiconductor substrate; the plasma is O2 plasma, and the The O2 plasma flow rate is controlled at 1-4Torr, and the power is controlled at 10-170W, which ca...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More