Defect operating system and device of semiconductor factory

An operating system and semiconductor technology, applied in semiconductor/solid-state device manufacturing, general control systems, control/regulation systems, etc., can solve problems such as poor performance, limited scanning electron microscope photography speed, and difficulty in finding failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

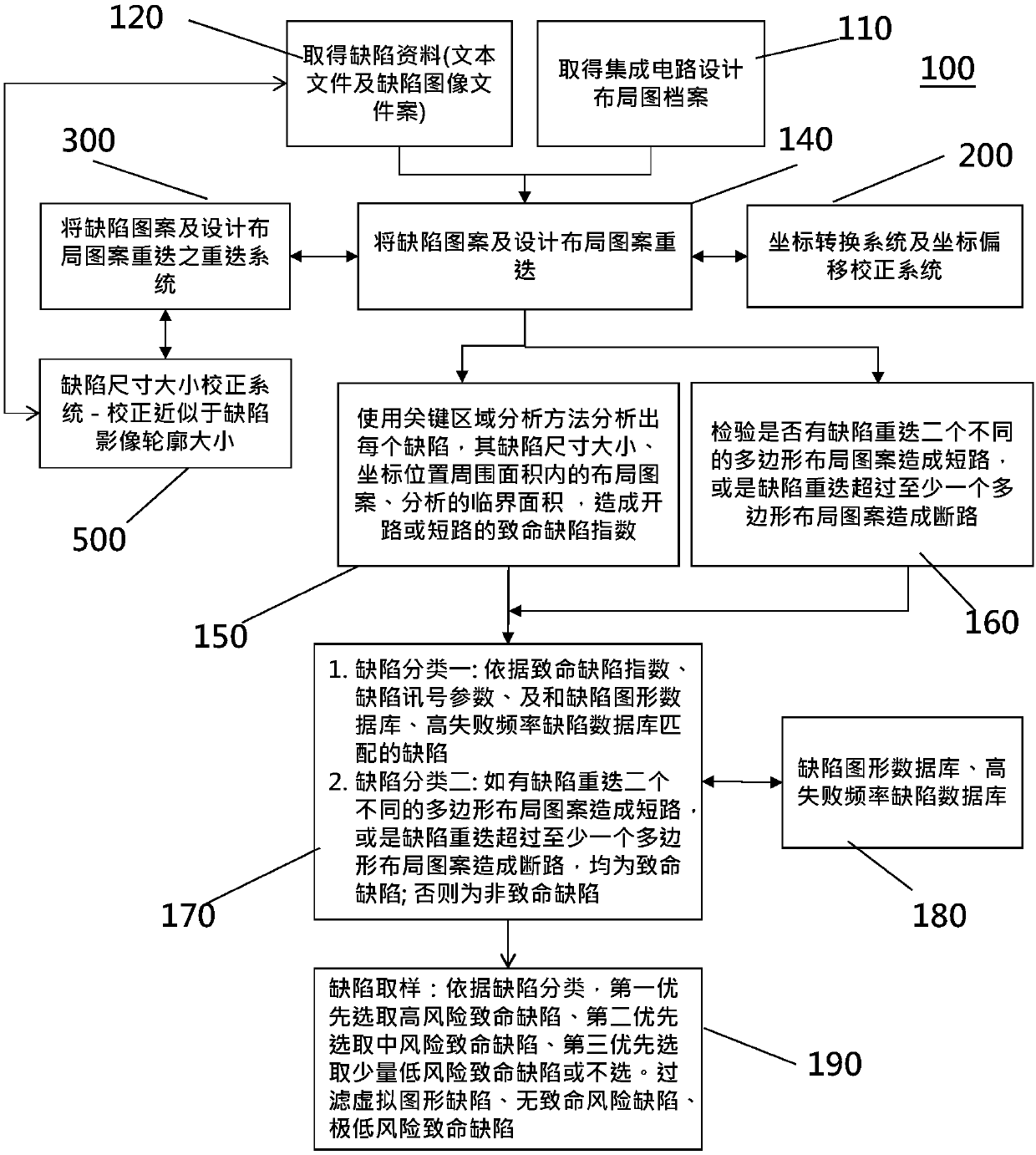

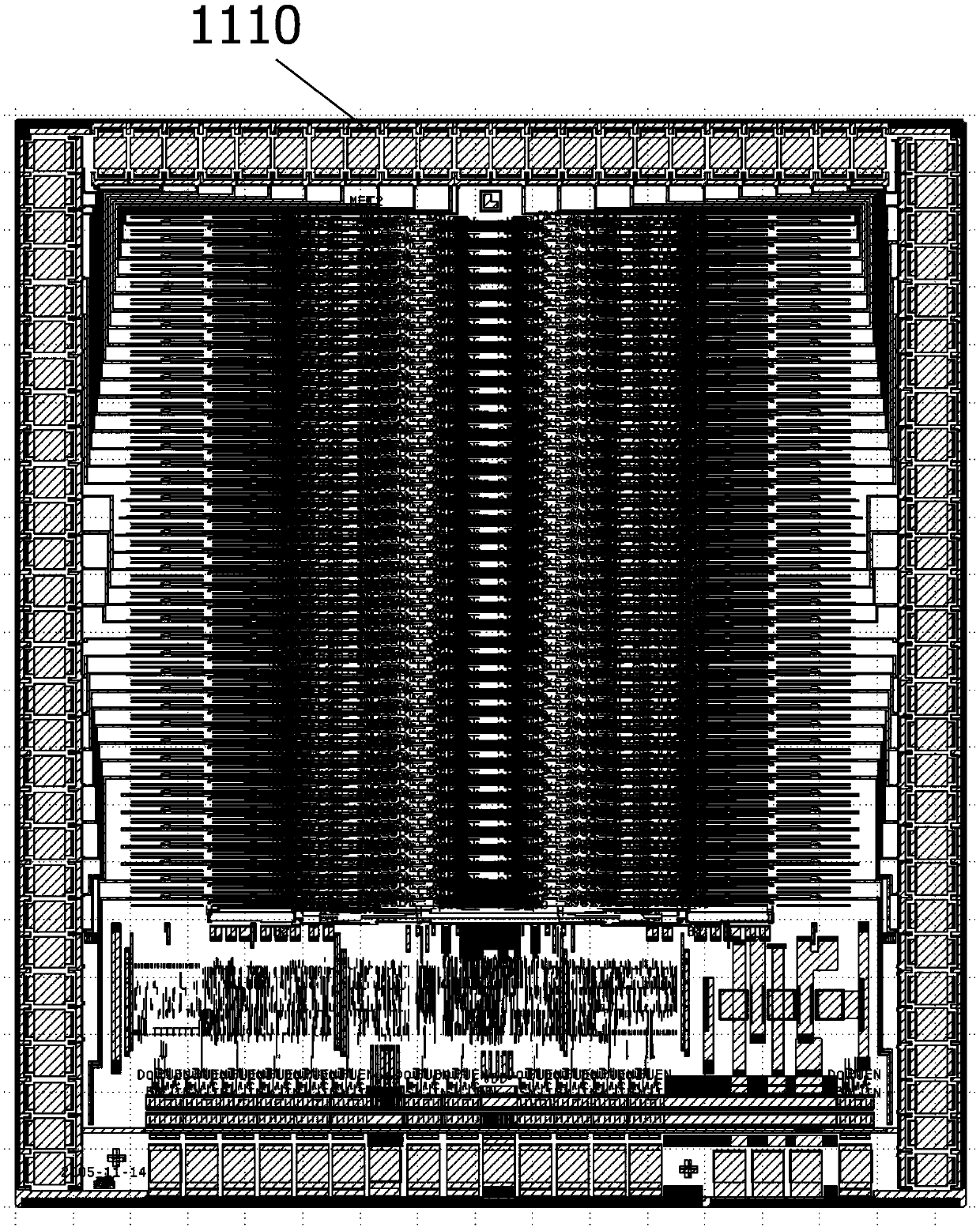

[0081] In semiconductor manufacturing plants, semiconductor packaging manufacturing plants, flat panel display manufacturing plants, solar panel manufacturing plants, printed circuit board manufacturing plants, photomask manufacturing plants, LED manufacturing or assembly plants, it is necessary to pass through photomasks, semiconductor lithography, Etching and thin film deposition and other equipment and process methods to form products with specific functions; due to many complicated steps in the manufacturing process, control of process and equipment parameters, deviation of equipment parameters, material and gas purity, or technical bottlenecks all cause Defects that affect product yield are unavoidable. Therefore, during the manufacturing process of semiconductor factories, defect detection and analysis are performed to improve yield and reduce costs.

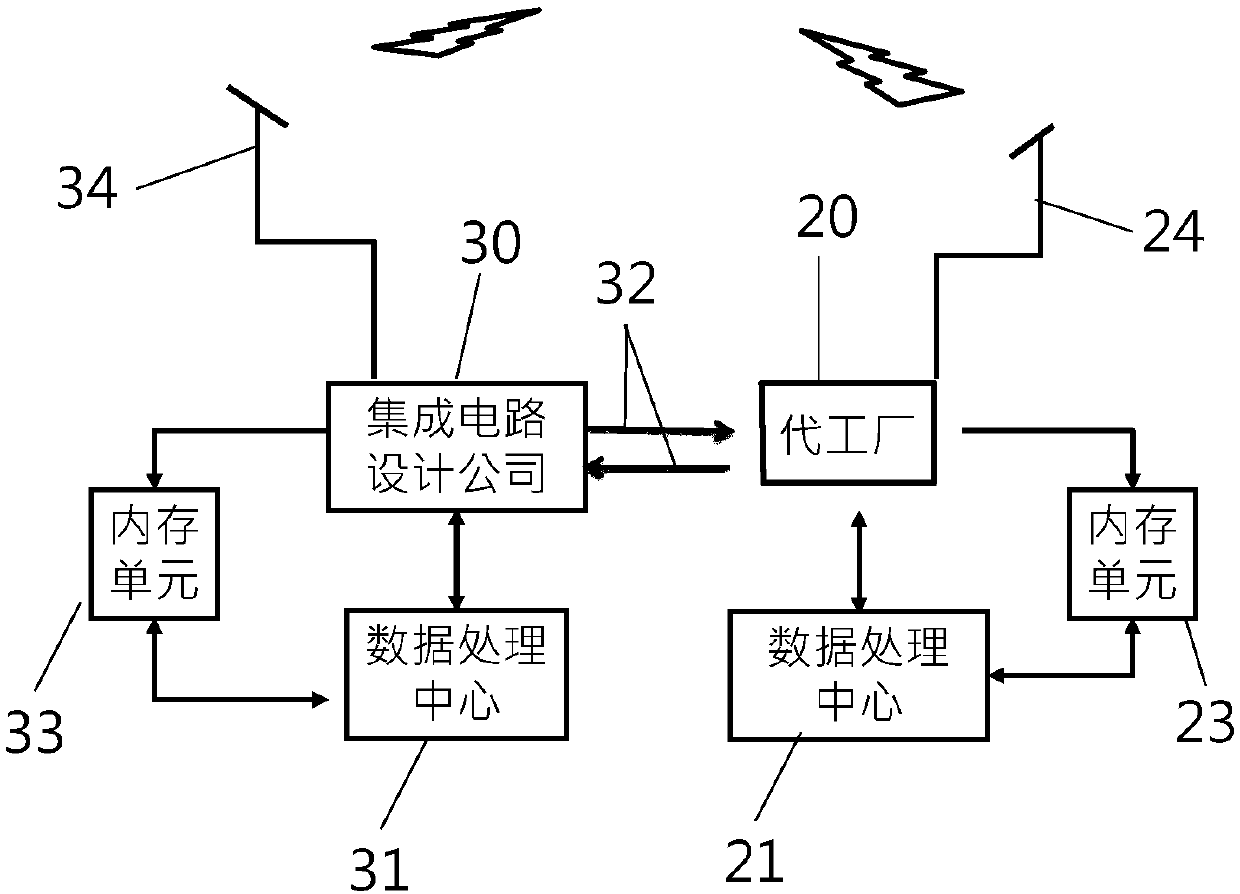

[0082] In addition, the "semiconductor factory defect operating system" described in the present invention includes: app...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More