Semiconductor interconnection structure and preparation method thereof

An interconnection structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as large resistance value of filling metal layer, reduction of driving resistance, and reduction of device driving resistance, etc. To achieve the best coverage of the ladder, slow down the top obstacles, and reduce the effect of resistance value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

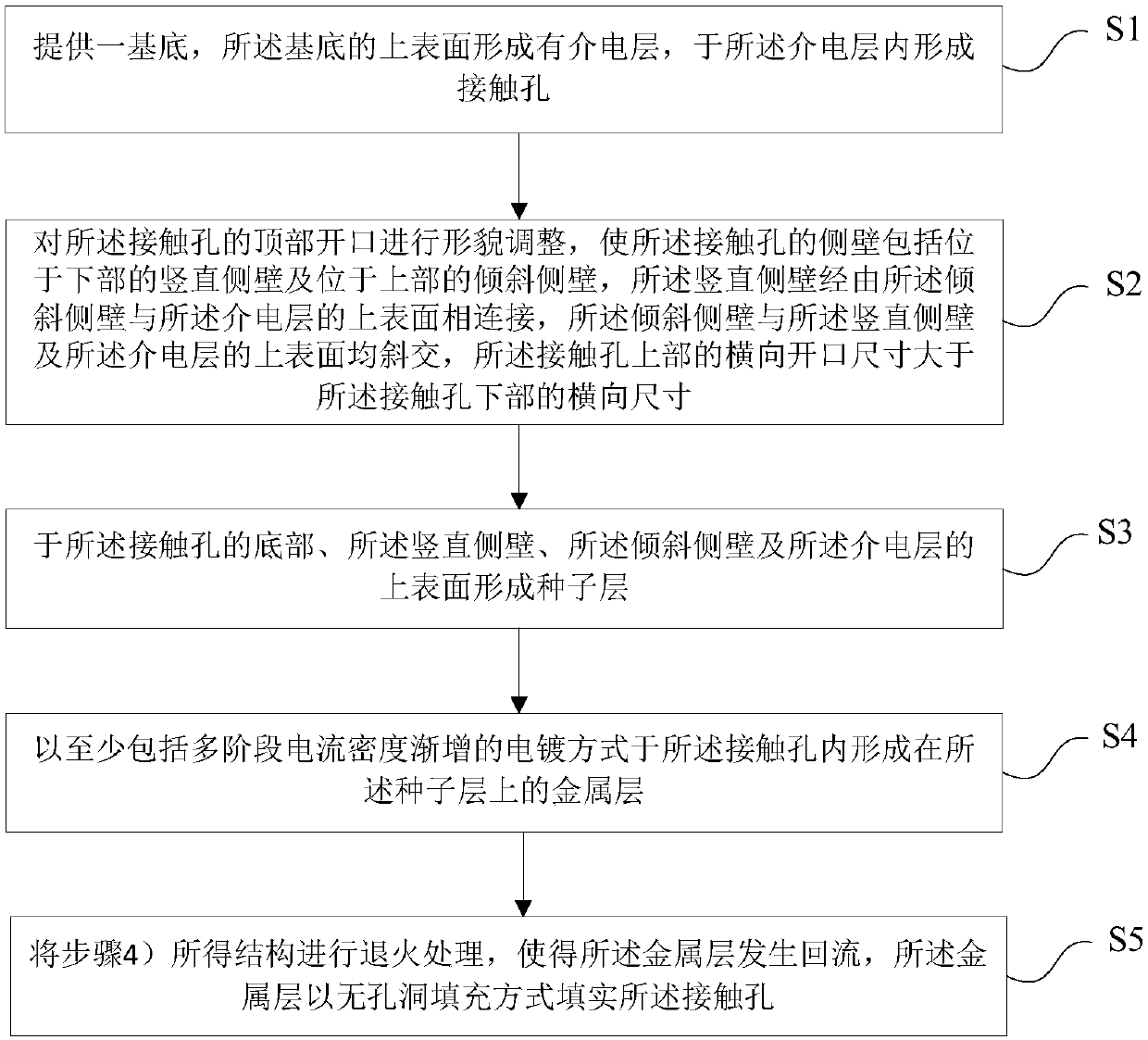

[0077] Such as figure 2 As shown, the present invention provides a method for preparing a semiconductor interconnection structure, and the method for preparing a semiconductor interconnection structure includes the following steps:

[0078] 1) A substrate is provided, a dielectric layer is formed on the upper surface of the substrate, and a contact hole is formed in the dielectric layer;

[0079] 2) Adjusting the shape of the top opening of the contact hole so that the sidewall of the contact hole includes a vertical sidewall at the lower part and an inclined sidewall at the upper part, and the vertical sidewall passes through the inclined sidewall. The wall is connected to the upper surface of the dielectric layer, the inclined side wall is oblique to the vertical side wall and the upper surface of the dielectric layer, and the lateral opening size of the upper part of the contact hole is larger than the The lateral dimension of the lower part of the contact hole;

[0080]...

Embodiment 2

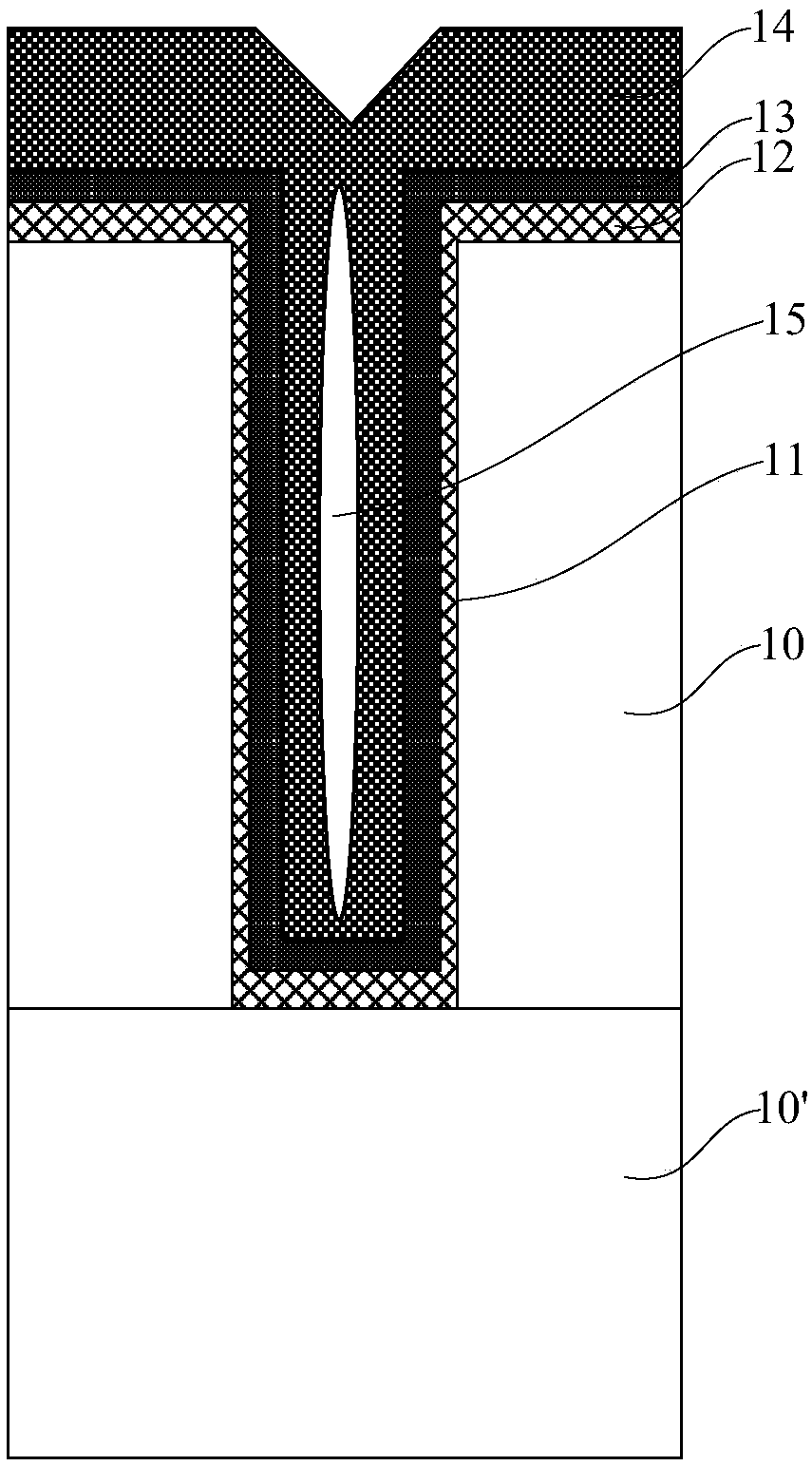

[0122] Please combine Figure 2 to Figure 9 read on Figure 10 to Figure 11 , the present invention also provides a semiconductor interconnection structure, the semiconductor interconnection structure comprising:

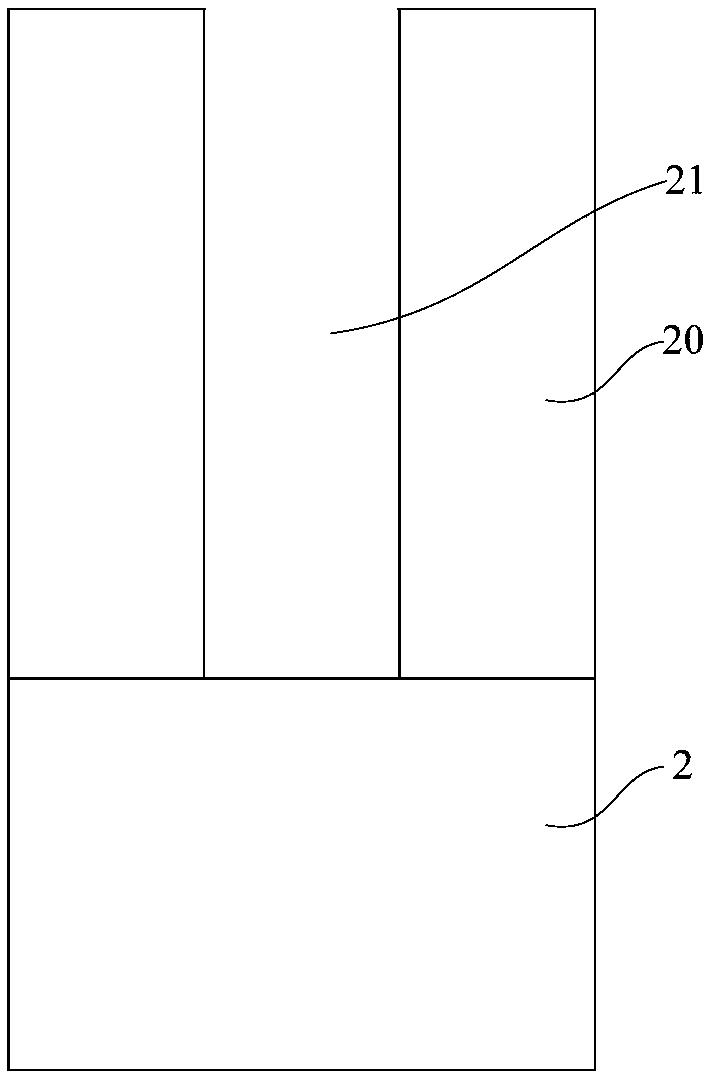

[0123] base2;

[0124] A dielectric layer 20, the dielectric layer 20 is located on the upper surface of the substrate 2, a contact hole 21 is formed in the dielectric layer 20, and the sidewall of the contact hole 21 includes a vertical sidewall 221 at the bottom And the inclined side wall 222 on the upper part, the vertical side wall 221 is connected with the upper surface of the dielectric layer 20 through the inclined side wall 222, the inclined side wall 222 is connected with the vertical side wall 221 and the upper surface of the dielectric layer 20 are oblique; the lateral opening size of the upper part of the contact hole 21 is larger than the lateral size of the lower part of the contact hole 21;

[0125] a seed layer 26, the seed layer 26 is formed on t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More