Insulating layer buried transistor structure and device

An insulating layer and transistor technology, applied in the direction of transistors, semiconductor devices, electrical components, etc., can solve the problems of substrate size limitation, large leakage current, low efficiency, etc., to improve the operating frequency range, improve operating power, and work efficiency Enhanced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

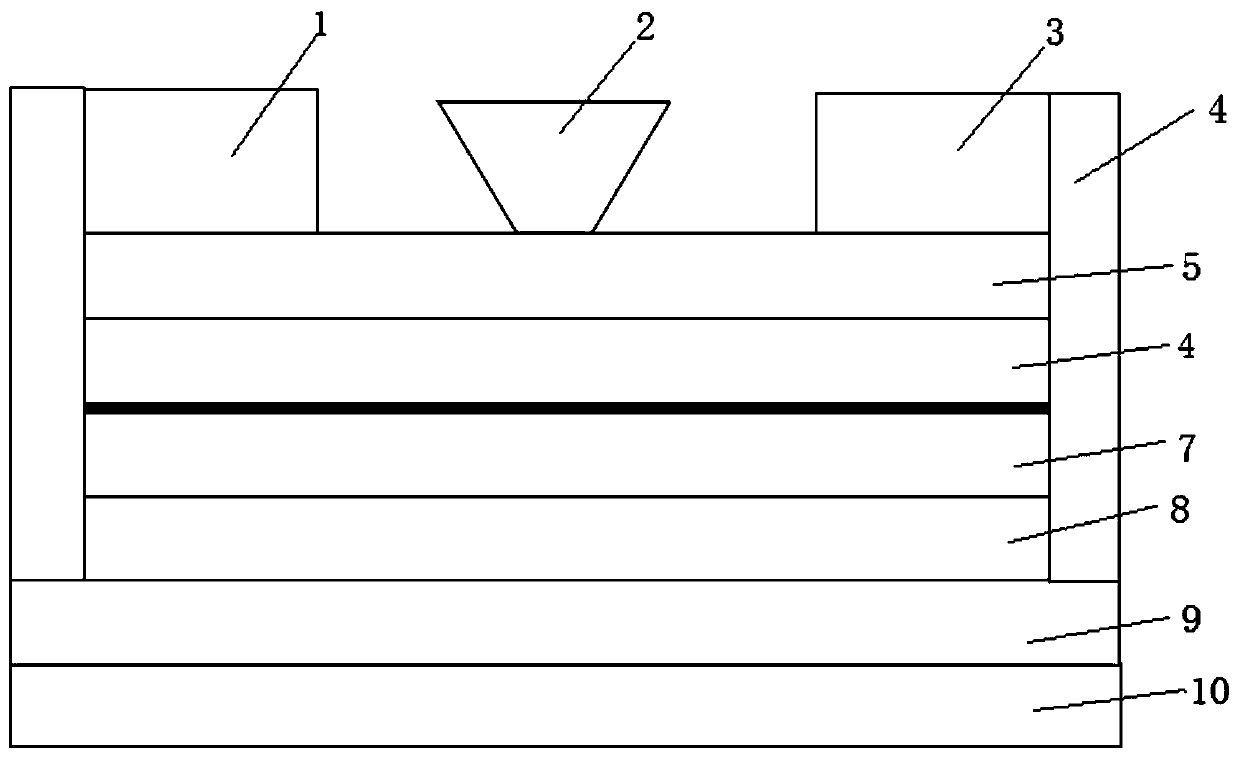

Embodiment 1

[0040]This embodiment discloses a transistor structure buried in an insulating layer 9, including a semiconductor substrate, a source 1, a gate 2, and a drain 3, and the semiconductor substrate includes a supporting substrate 10, a channel layer 7, and an isolation layer 4 and a barrier layer 5, the channel layer 7, the isolation layer 4 and the barrier layer 5 are all III-V group compound semiconductor film layers, and the channel layer 7, The isolation layer 4 and the barrier layer 5; the source 1 and the drain 3 are arranged on both sides of the barrier layer 5 and are in contact with the barrier layer 5; the gate 2 is arranged on the source 1 Between the drain electrode 3 and the barrier layer 5; an insulating layer 9 is provided between the supporting substrate 10 and the channel layer 7; the insulating layer 9 is an oxide layer; on the supporting substrate 10 An insulating layer 9 is arranged between the channel layer 7, which is mainly used to block substrate leakage, i...

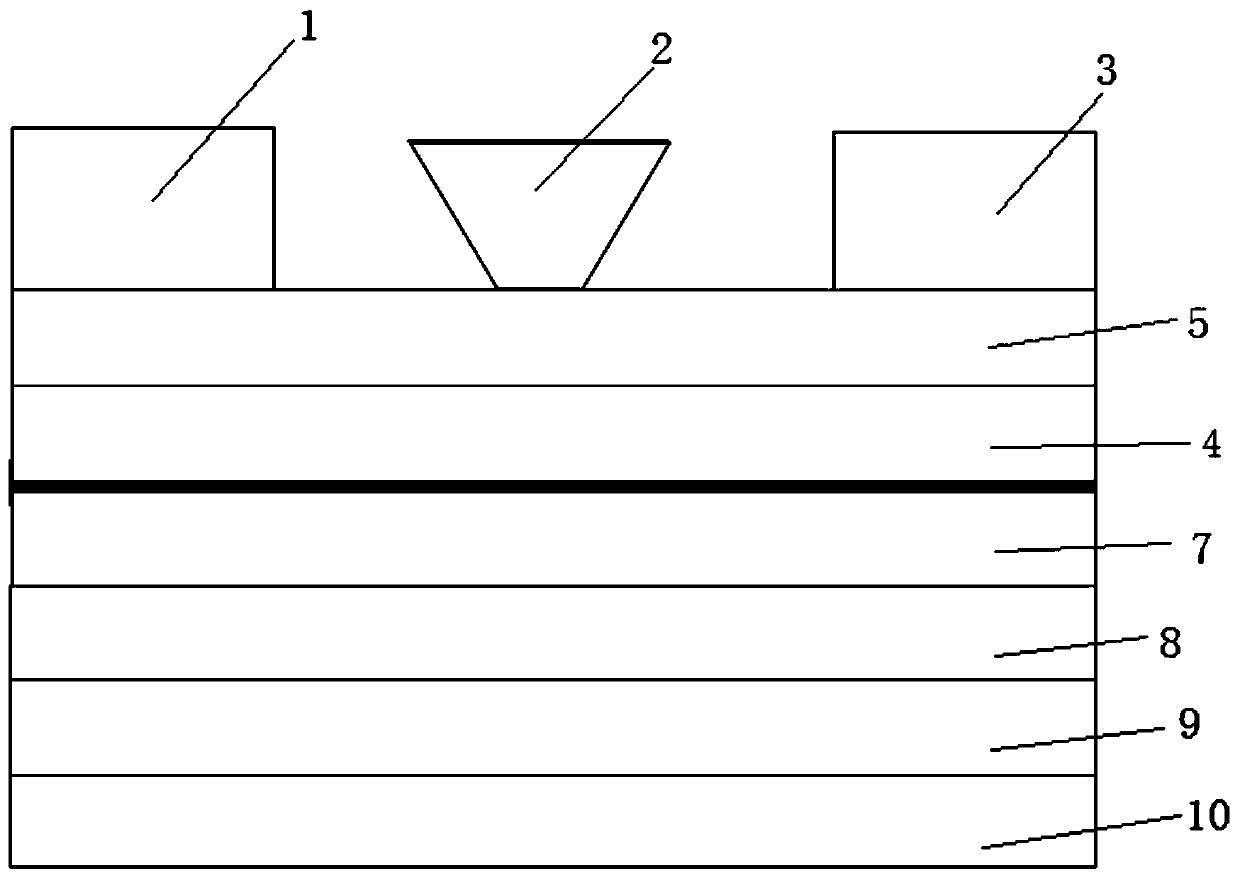

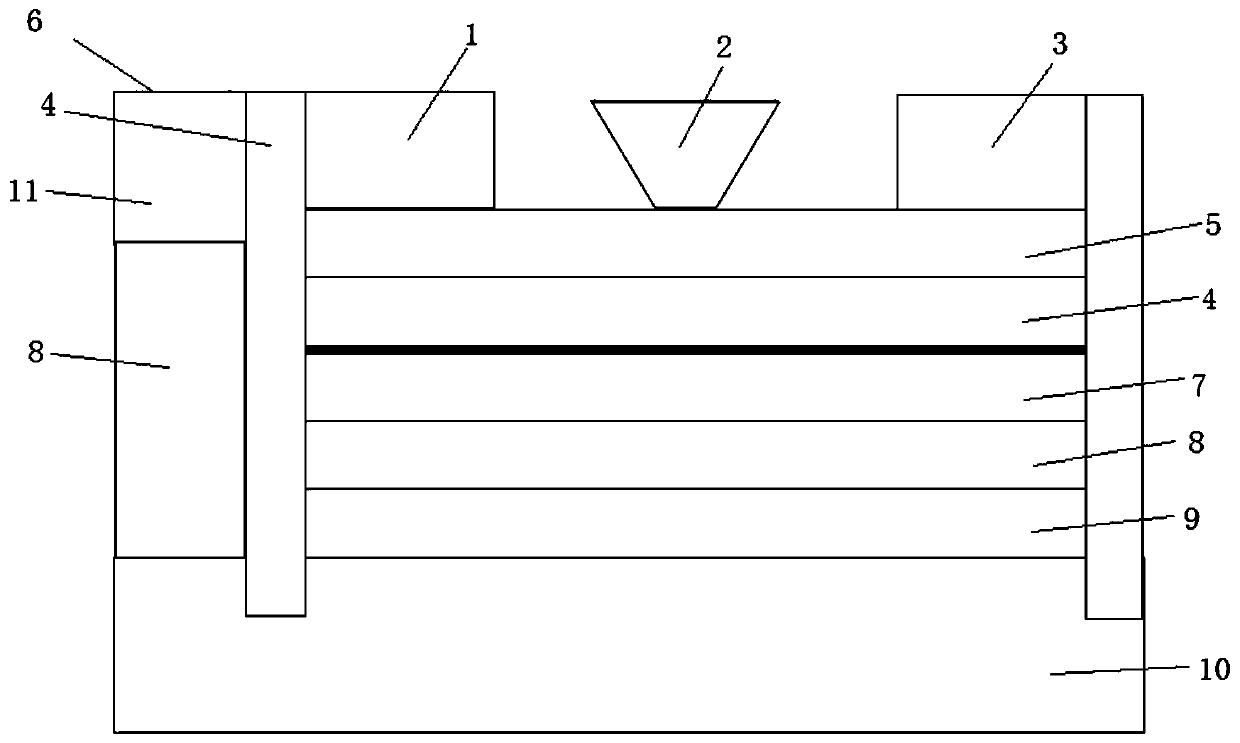

Embodiment 2

[0042] This embodiment is based on the first embodiment, and discloses a transistor structure buried with insulating layers 9, the insulating layers 9 and the buffer layers 8 are arranged alternately; the insulating layers 9 are provided with at least one layer; the The buffer layer 8 is provided with at least one layer; the back gate control electrode 12 includes a contact layer 11 and a buffer layer 8; the contact layer 11 is grown on the buffer layer 8, and the back gate control electrode 12 is provided with a buffer layer 8, A layer of buffer layer 8 is arranged on the insulating layer 9, and two layers of buffer layer 8 are arranged, mainly for the transition and buffering of growing high-quality crystals, avoiding the occurrence of crystal cracks and deformation caused by direct growth of crystals, and the material of buffer layer 8 The lattice constant is between the lattice constants of the semiconductor material of the channel layer 7 and the semiconductor material of ...

Embodiment 3

[0044] This embodiment is based on Embodiment 1 and Embodiment 2, and discloses a scene switching in transistors realized by controlling the threshold of the back gate gate, using the level of the threshold voltage of the back gate gate 12 transistors to substantially adapt to different The application environment, and the level of the threshold voltage required by different scenarios is controlled through the back gate, and different scenarios are switched. It can be widely used in different scenarios such as the 5th generation mobile communication and the Internet of Everything IoT.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More