Patterned hard mask layer preparation method, capacitor array structure and preparation method thereof

A hard mask layer, hard mask technology, applied in the direction of electrical solid devices, circuits, electrical components, etc., can solve the problems of electrical connection and isolation, affecting memory performance, component size reduction, etc. Reduced misalignment issues, good functional effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

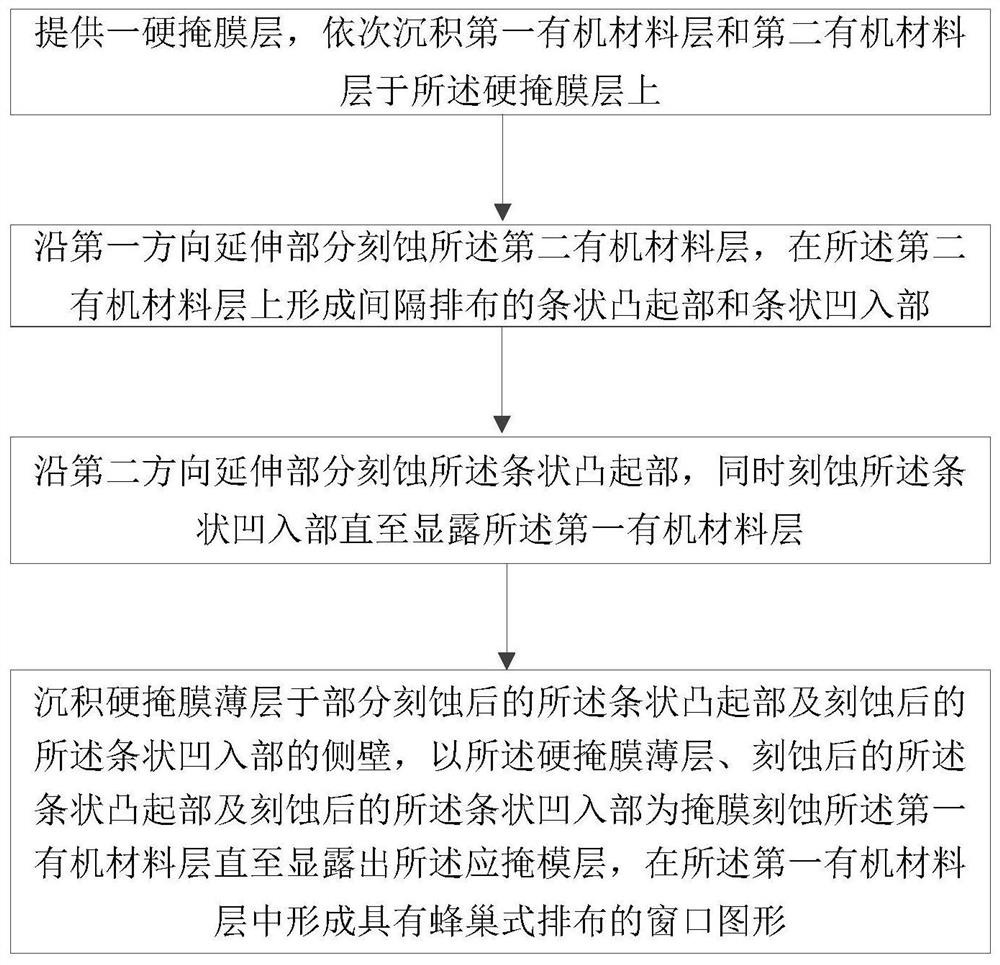

[0115] This embodiment provides a method for preparing a patterned hard mask layer. Such as figure 1 As shown, the method of the present embodiment includes the following steps:

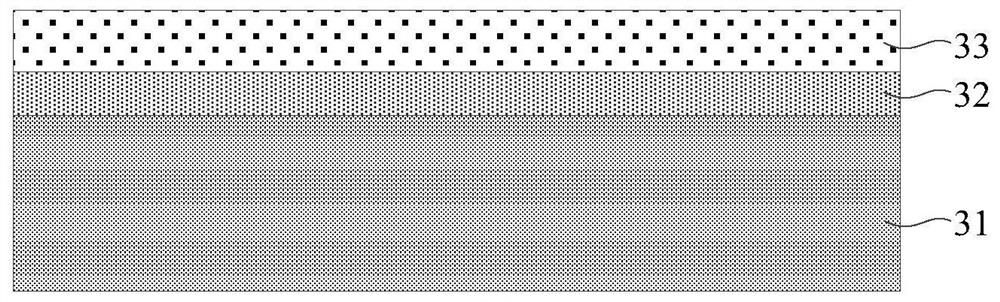

[0116] providing a hard mask layer, sequentially depositing a first organic material layer and a second organic material layer on the hard mask layer;

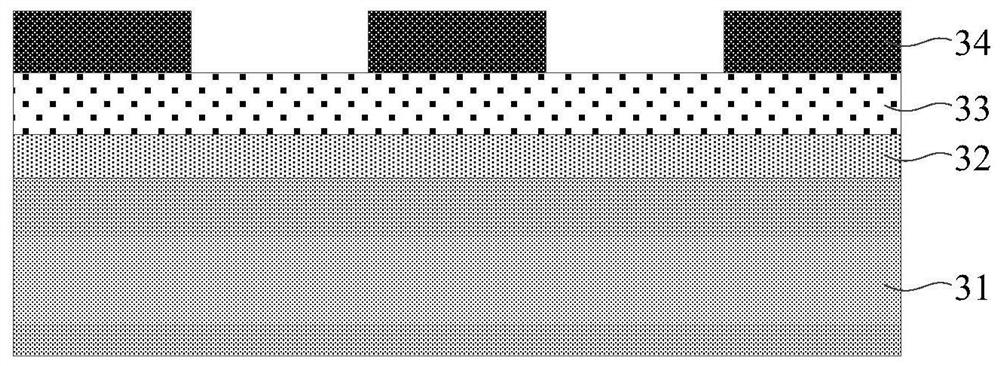

[0117] Etching the second organic material layer along a portion extending along the first direction, forming strip-shaped protrusions and strip-shaped recesses arranged at intervals on the second organic material layer;

[0118] Etching the strip-shaped protrusion part along the second direction, and etching the strip-shaped concave part at the same time until the first organic material layer is exposed;

[0119] Depositing a hard mask thin layer on the partially etched strip-shaped protrusions and the sidewalls of the etched strip-shaped concave portions, using the hard mask thin layer and the etched strips The strip-shaped convex portion and th...

Embodiment 2

[0140] This embodiment provides a method for preparing a capacitor array structure, such as Figure 28 As shown, the method of the present embodiment includes the following steps:

[0141] A semiconductor substrate is provided, the semiconductor substrate includes a plurality of capacitive contact nodes located in the memory array structure, the first and second sacrificial layers, the middle supporting layer, the third sacrificial layer and the upper supporting layer are sequentially formed on the semiconductor substrate layer, and depositing a barrier layer over the second support layer;

[0142] A patterned hard mask layer with windows arranged in a honeycomb arrangement is formed on the above structure, and based on the patterned hard mask layer, the barrier layer, the second supporting layer, the second sacrificial layer, the first The support layer and the first sacrificial layer are used to form a capacitor hole corresponding to the window, and the capacitor hole expos...

Embodiment 3

[0151] This embodiment also provides a method for preparing a capacitor array structure. The similarities between this embodiment and Embodiment 2 will not be repeated, and the difference lies in:

[0152] The method described in this embodiment also includes, as Figure 32 As shown, conductive material is deposited on the bottom and sidewall of the capacitor hole 20 to form the capacitor bottom electrode 10 , and then the first sacrificial layer 22 , the second sacrificial layer 23 , the third sacrificial layer 25 and the barrier layer 27 are removed. Then, if Figure 33 As shown, a capacitor dielectric layer 11 is deposited and formed on the inner surface of the capacitor lower electrode 10 and the exposed outer surface, an upper electrode inner lining layer 12 is formed on the surface of the capacitor dielectric layer 11, and an upper electrode inner lining layer 12 is formed on the surface of the upper electrode inner lining layer 12. The hole-filling body 13 for the uppe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More