Silicon carbide MOSFET and preparation method thereof

A technology of silicon carbide and silicon carbide substrates, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as increasing field strength, SiC MOSFET needs to be improved, and low electron mobility in the inversion layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] Preparation methods include:

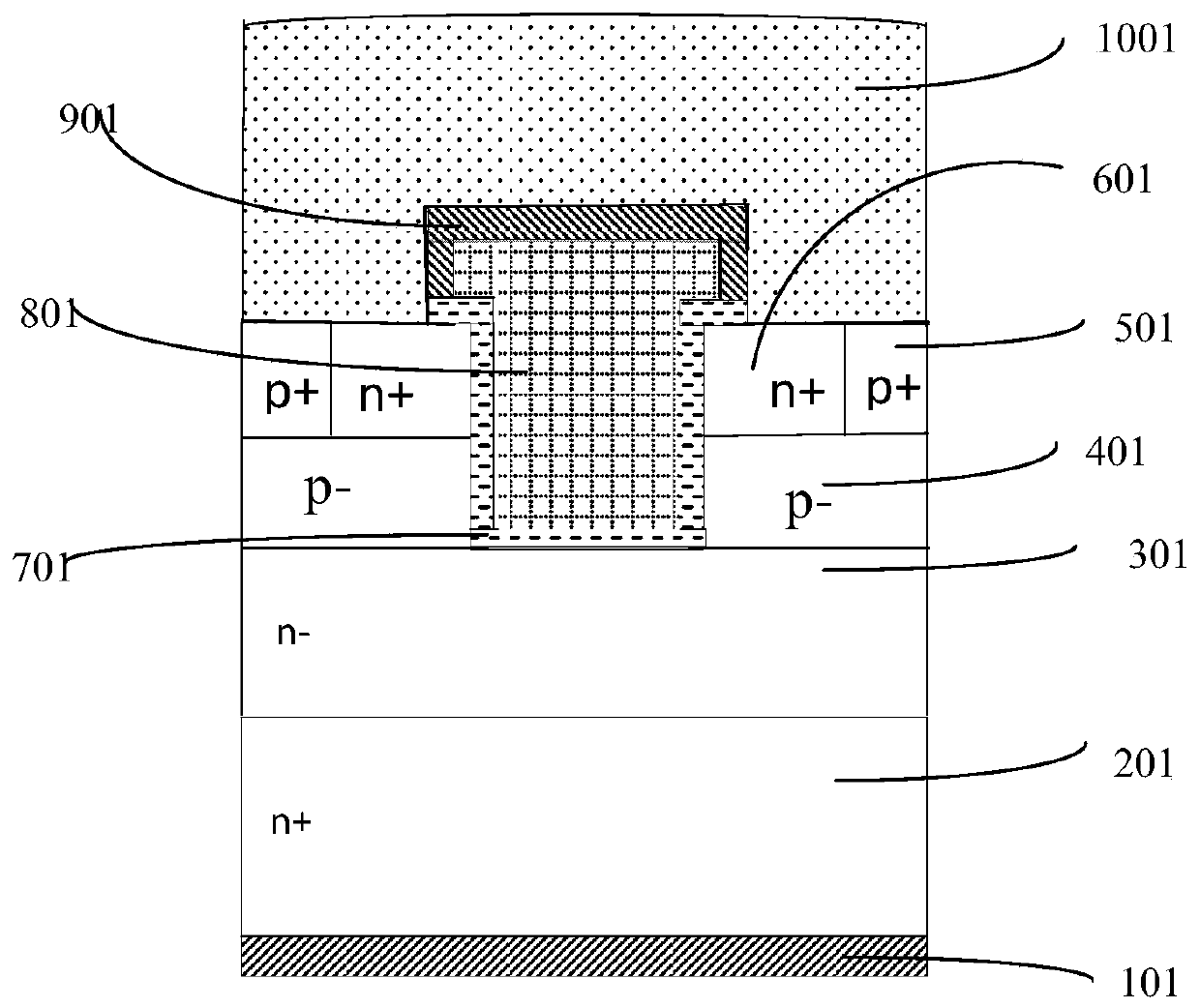

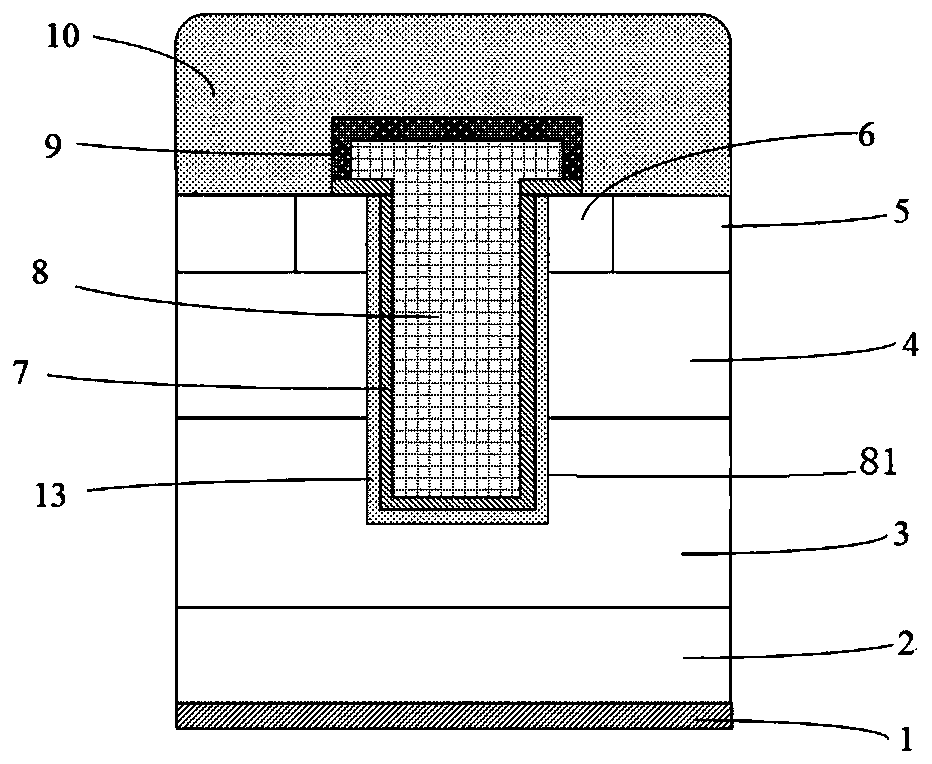

[0050] Step 1: On the heavily doped n+ type SIC substrate 2, the first epitaxial layer 31 of n-type SIC is epitaxially formed by PECVD; the doping concentration of the first epitaxial layer 31 is 1×10 15 cm -3 , the thickness is 10 microns, the doping impurity is nitrogen (N), and the structural diagram is shown in Figure 5 .

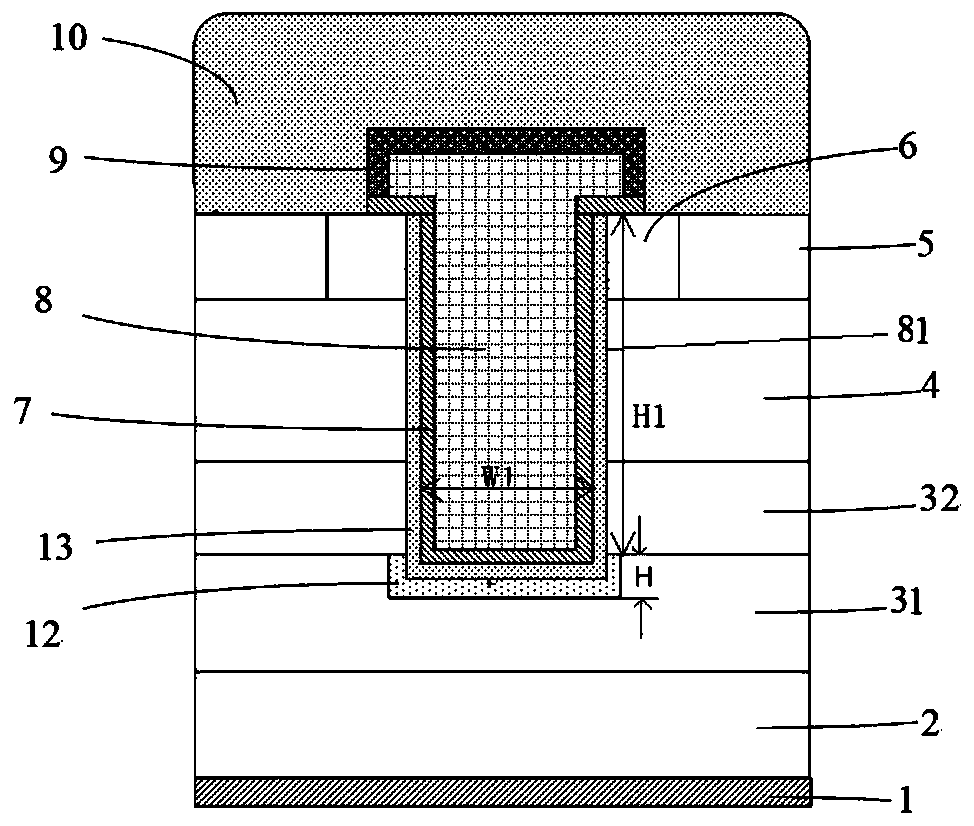

[0051] Step 2: Etching the n-type first epitaxial layer 31 to form a step profile, the etching depth is 0.1 micron, see the structure schematic diagram Figure 6 .

[0052] Step 3: Epitaxially form a heavily doped p+ epitaxial layer 121 on the etched n-type first epitaxial layer 31 and perform etching to form the p+ heavily doped region 12; the p+ heavily doped region 12 The doping concentration is 1×10 16 cm -3 , the doping impurity is aluminum (Al), and the thickness is 1 micron; Figure 7 , Figure 8 shown.

[0053] Step 4: Continue epitaxially forming an n-lightly doped second epitaxial layer 32 on the...

Embodiment 2

[0062] Preparation methods include:

[0063] Step 1: On the heavily doped n+ type SIC substrate 2, an n-type SIC epitaxial layer 3 is formed by MOCVD epitaxy; the doping concentration of the epitaxial layer 3 is 5×10 15 cm -3 , the thickness is 15 microns, the dopant impurity is nitrogen (N), and the structural diagram is shown in Figure 4 .

[0064] Step 2: Epitaxially form a p-type epitaxial layer 4 on the n-type epitaxial layer 3; the doping concentration of the p-type SIC lightly doped epitaxial layer 4 is 5×10 13 cm -3 , the doping impurity is aluminum (Al), and the thickness is 2.5 microns; if Figure 4 shown;

[0065] Step 3: forming n+ source region 6 and p+ contact region 5 on epitaxial layer 4 by photolithography and implantation; the doping concentration of source region 6 is 1×10 15 cm -3 , the doping concentration of the contact region 5 is 5×10 15 cm -3 ; and carry out high temperature annealing after implantation, the annealing temperature is between 1...

Embodiment 3

[0072] Preparation methods include:

[0073] Step 1: On the heavily doped n+ type SIC substrate 2, the first epitaxial layer 31 of n-type SIC is epitaxially formed by PECVD; the doping concentration of the first epitaxial layer 31 is 1×10 16 cm -3 , the thickness is 15 microns, the dopant impurity is nitrogen (N), and the structural diagram is shown in Figure 5 .

[0074] Step 2: Etching the n-type first epitaxial layer 31 to form a step profile, the etching depth is 0.4 microns, see the structure schematic diagram Figure 6 .

[0075] Step 3: Epitaxially form a heavily doped p+ epitaxial layer 121 on the etched n-type first epitaxial layer 31 and perform etching to form the p+ heavily doped region 12; the p+ heavily doped region 12 The doping concentration is 1×10 17 cm -3 , the doping impurity is aluminum (Al), and the thickness is 2 microns; as Figure 7 , Figure 8 shown.

[0076] Step 4: Continue epitaxially forming an n-lightly doped second epitaxial layer 32 o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More