Power semiconductor device and manufacturing method thereof

A technology of power semiconductors and manufacturing methods, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as high process costs, low integration of semiconductor devices, and poor electrical performance of power semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

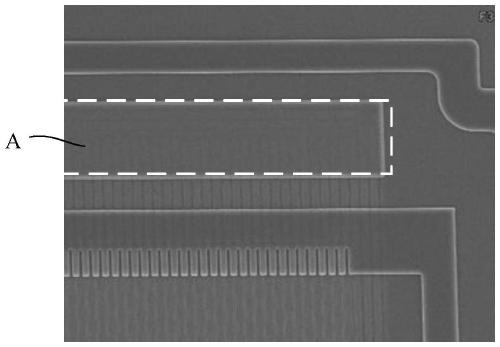

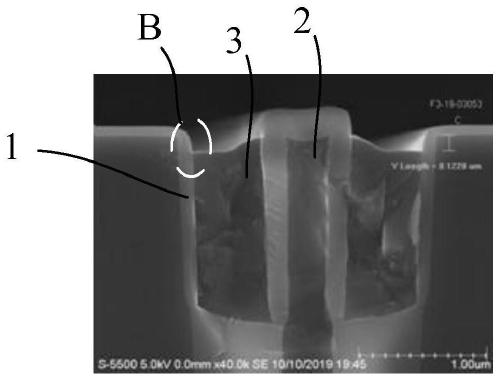

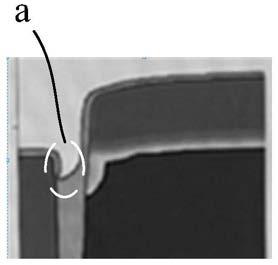

[0043] As mentioned in the background technology, when the gate polysilicon of power semiconductor devices is formed, the problem of inconsistency of the gate polysilicon layer is prone to occur due to the equipment manufacturing process, resulting in poor uniformity of the degree of over-etching of the gate polysilicon layer of the wafer. ,Such as Figure 1b As shown, the thinning of the gate oxide layer tends to occur at the position B of the gate oxide layer 1 on the side of the gate polysilicon layer (gate poly) 3 away from the shield gate polysilicon 2, specifically as Figure 1c As shown, there is a longitudinal defect groove a at the position B of the gate oxide layer 1, and the defect groove a makes the ion implantation process (first p-type ion doping, and then N-type ion doping) when forming the source Doping, the p-type ion-doped region is located below the N-type ion-doped region), N-type ions are implanted into the gate oxide layer 1, which reduces the characteris...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More