Nanowire ion grid control synaptic transistor and preparation method thereof

A nanowire and transistor technology, applied in the field of ion gate control synapse transistor and its preparation, can solve the problems of large area cost of synapse devices, poor CMOS process compatibility, poor device consistency, etc., and achieves good CMOS back-end integration characteristics, The effect of spatiotemporal signal integration and good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The present invention will be described in detail below through specific examples in conjunction with the accompanying drawings.

[0053] Nanowire ion-gated synaptic transistors were fabricated according to the following steps:

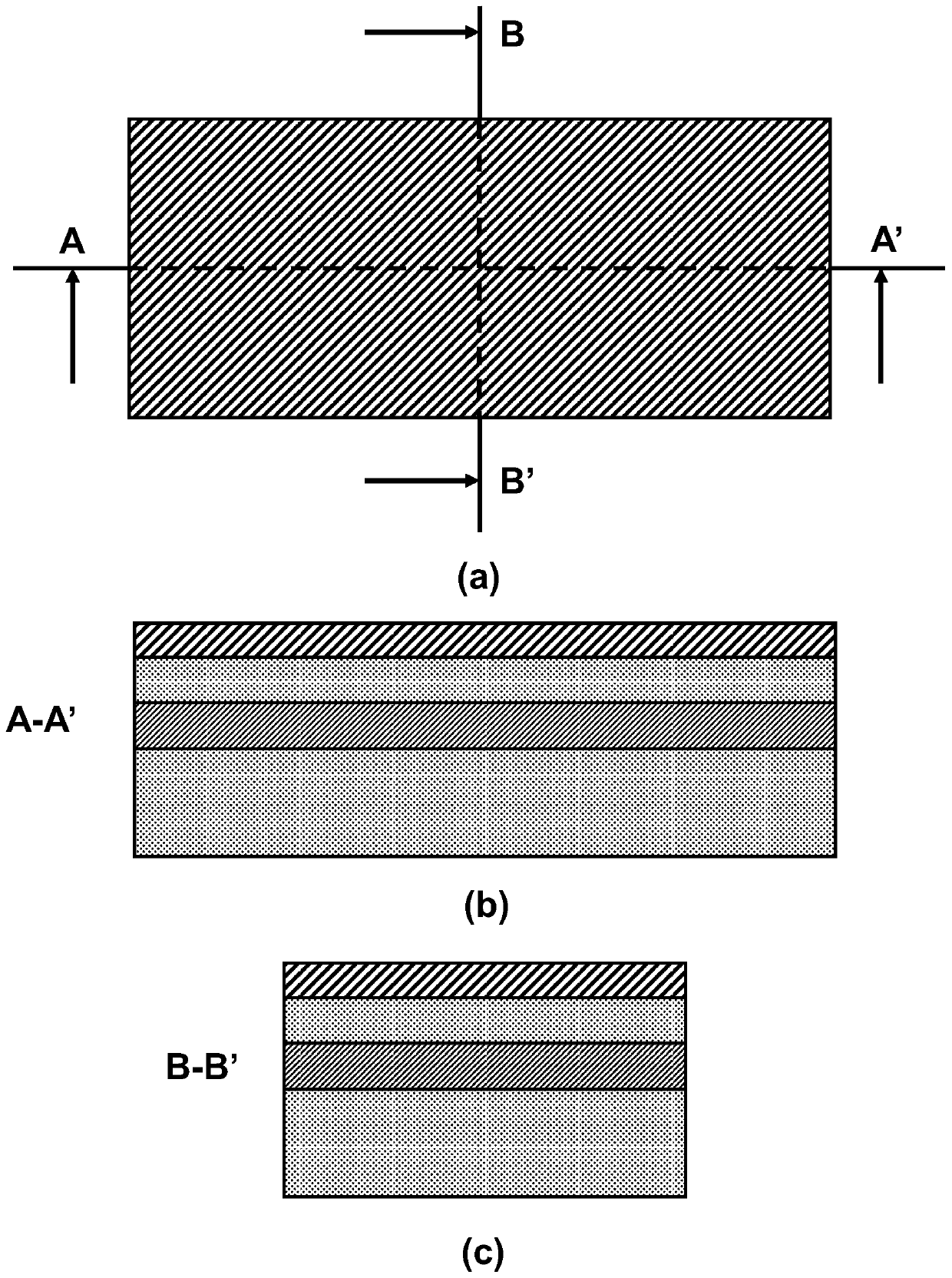

[0054] 1) Perform dry oxygen oxidation or hydrogen-oxygen synthesis oxidation on the SOI substrate to oxidize the silicon film to silicon oxide, then use hydrofluoric acid (HF) solution to bleach the silicon oxide layer, and finally thin the silicon film to 40nm, spin-coat HSQ electron beam glue on the thinned silicon film surface, such as figure 1 shown;

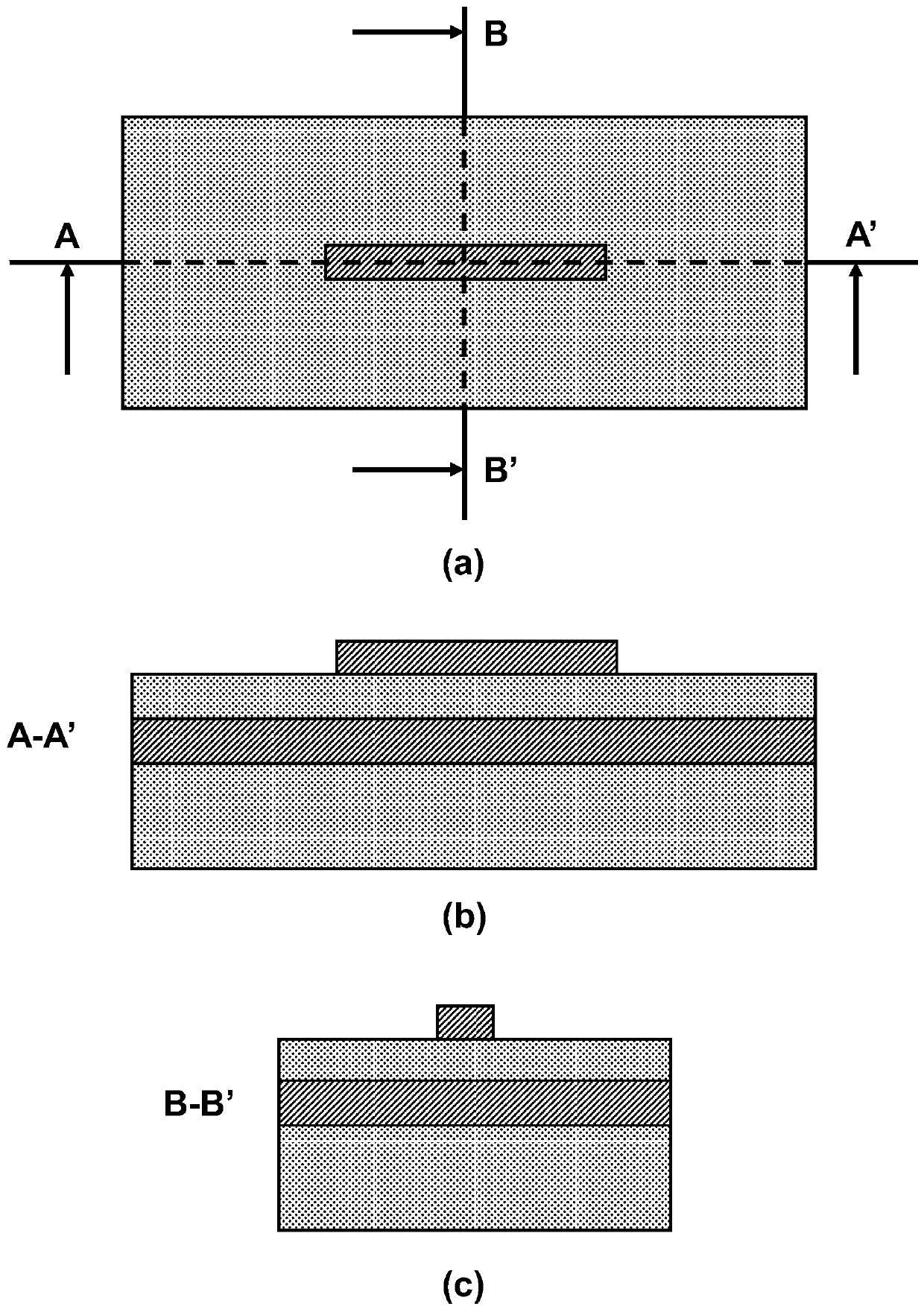

[0055] 2) A silicon nanowire with a groove length of 13 μm and a diameter of 40 nm is defined by an electron beam, such as figure 2 shown;

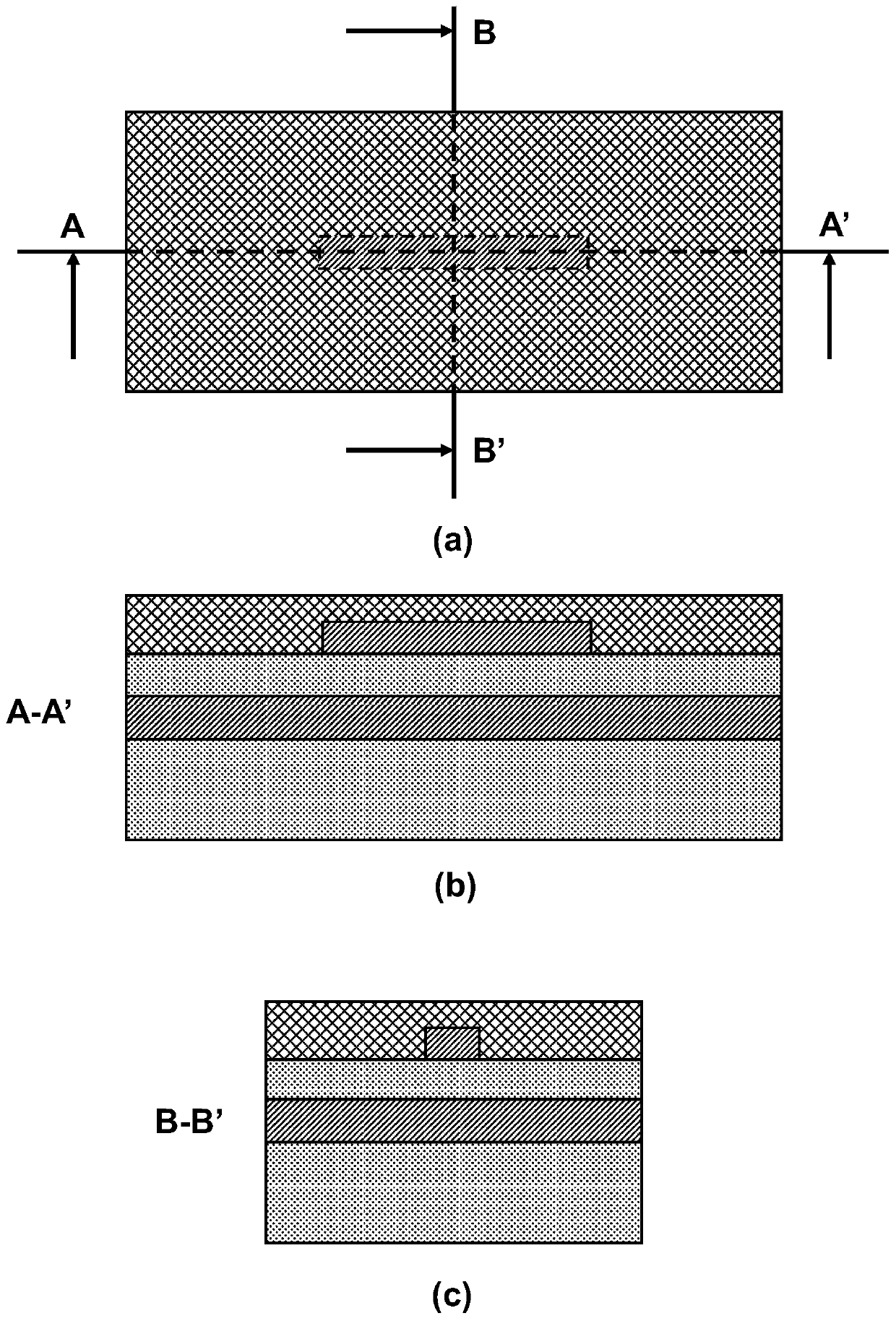

[0056] 3) Spin-coat organic positive photoresist, define the source and drain gates by photolithography, and inductively coupled plasma etching (Inductively Coupled Plasma, ICP) etch the silicon film to the silicon oxide BOX layer, such as image ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More