Novel InAs-GaSb TFET suitable for planar process

A planar process and a new type of technology, applied in the field of microelectronics, can solve the problems of difficult compatibility of planar process, complicated preparation process, and easy breakage of the channel, and achieve the effect of flexible matching design, simple preparation process, and guaranteed interface quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

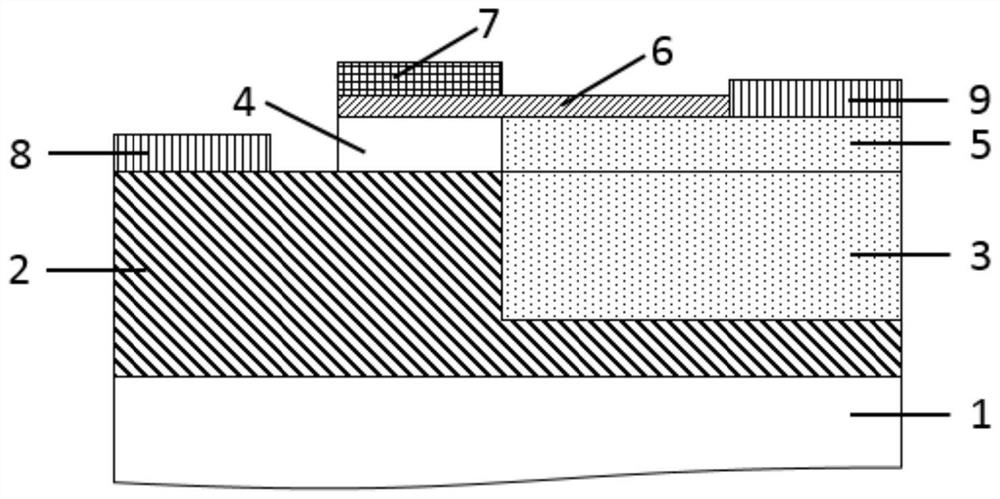

[0037] See figure 1 , figure 1 It is a schematic structural diagram of a novel InAs-GaSb TFET suitable for a planar process provided by an embodiment of the present invention. As shown, the device includes:

[0038] substrate1;

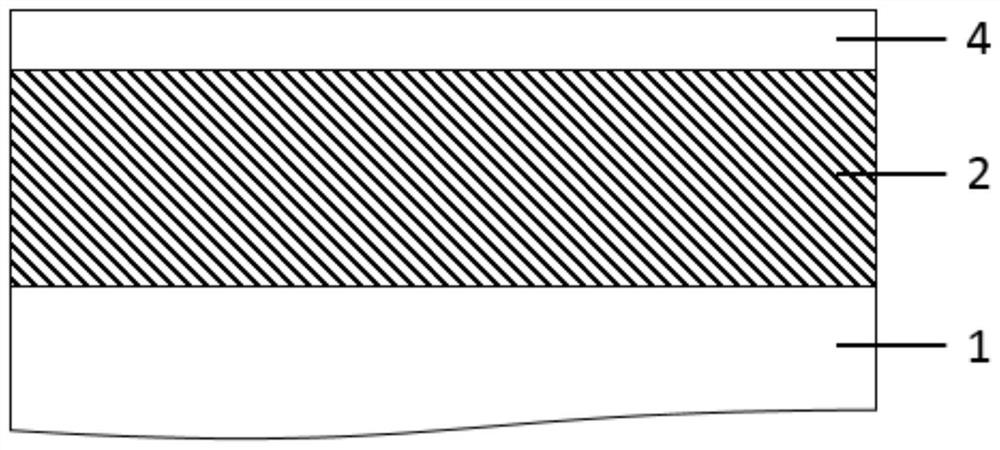

[0039] The source region 2 is disposed on the substrate 1;

[0040] The first drain region 3 is disposed on the substrate 1 and located in the source region 2;

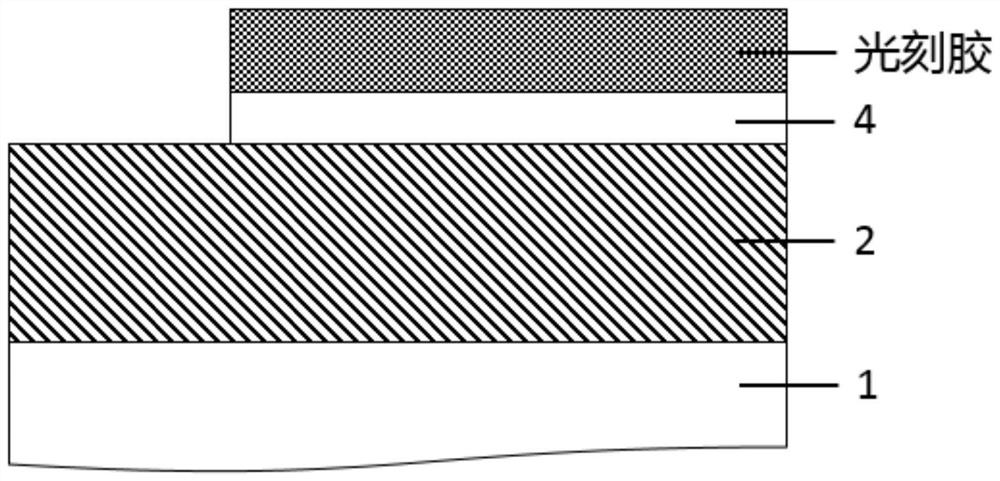

[0041] a channel layer 4, disposed on the source region 2;

[0042] The second drain region 5 is arranged on the first drain region 3;

[0043] a gate dielectric layer 6 disposed on the channel layer 4 and the second drain region 5;

[0044] The gate 7 is arranged on the gate dielectric layer 6;

[0045] The source 8 is arranged on the source region 2;

[0046] The drain 9 is arranged on the second drain region 5 .

[0047] In this embodiment, the interface between the source 8 and the source region 2 is an ohmic contact, the interface between the drain 9 and the second drain region ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More