Anti-fuse memory cell and manufacturing method thereof

A technology of memory cells and manufacturing methods, applied in the field of semiconductors, capable of solving problems such as damage to select gate structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] It can be seen from the background art that the selection gate dielectric layer in the antifuse memory cell in the prior art is prone to damage.

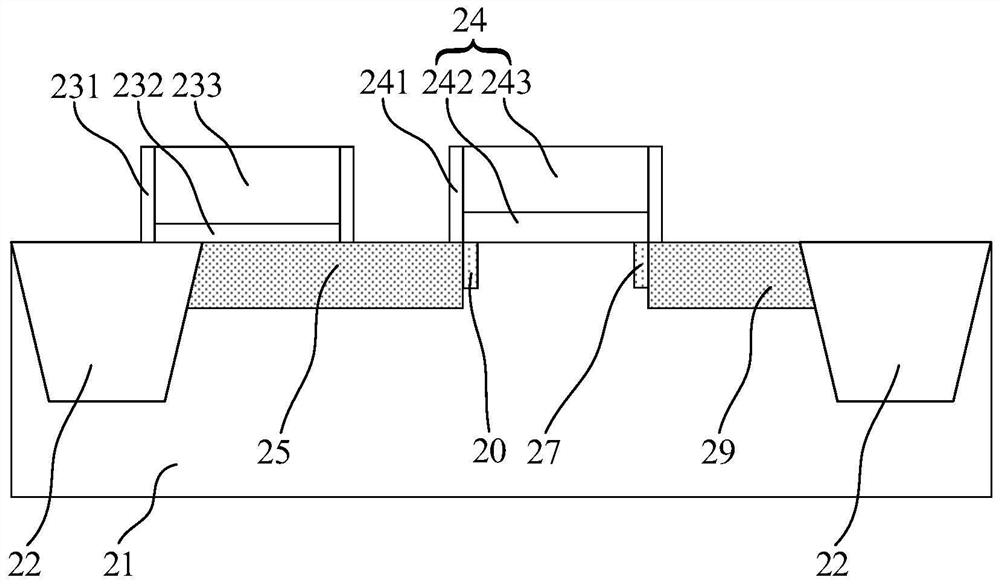

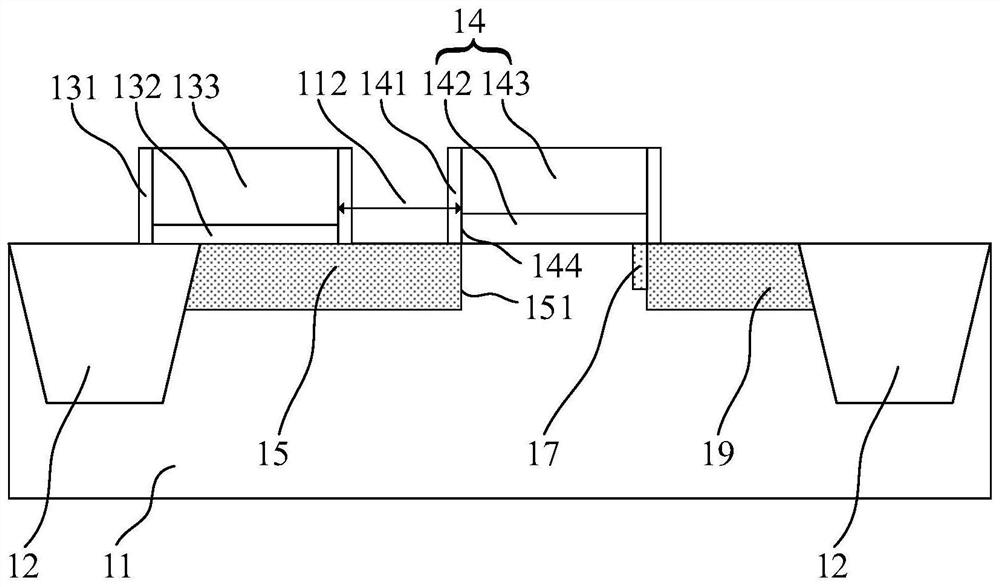

[0025] refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of an antifuse memory cell. refer to figure 1 , the antifuse memory unit comprises: a substrate 21 with a select gate structure 24 on the substrate; a first doped region 25 and a second doped region 29, the first doped region 25 and the second doped region 29 respectively In the substrate 21 located on opposite sides of the select gate structure 24, the doping ion types of the first doped region 25 and the second doped region 29 are the same; the antifuse gate dielectric layer located on the first doped region 25 232 and the antifuse gate 233 located on the antifuse gate dielectric layer 232; the third doped region 27, the third doped region 27 is located between the second doped region 29 and the select gate structure 24, the third Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More