Memory and forming method thereof

A memory and graphics technology, applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problem of high dielectric constant, affecting signal transmission speed and strength, coupling effect of metal bit lines and capacitive contact lines, etc. problem, achieve the effect of small dielectric constant, improve isolation performance, and reduce parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The specific implementation of the memory provided by the present invention and its forming method will be described in detail below in conjunction with the accompanying drawings.

[0025] Please refer to Figure 1A to Figure 12 It is a structural schematic diagram of the forming process of the memory according to a specific embodiment of the present invention.

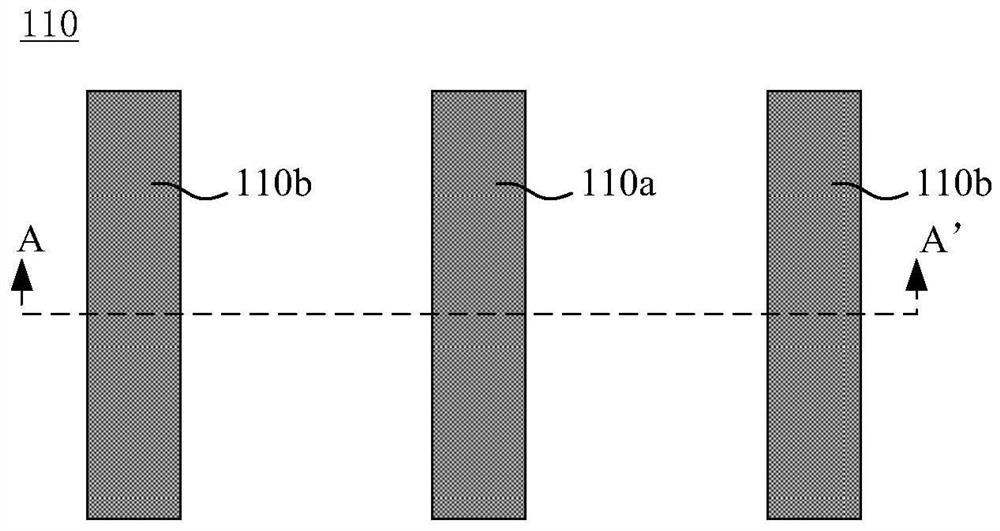

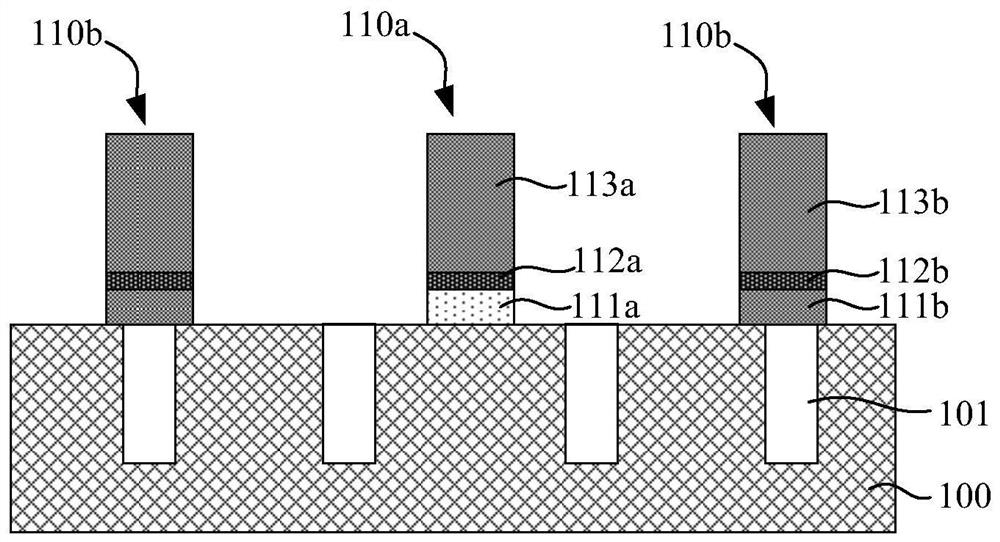

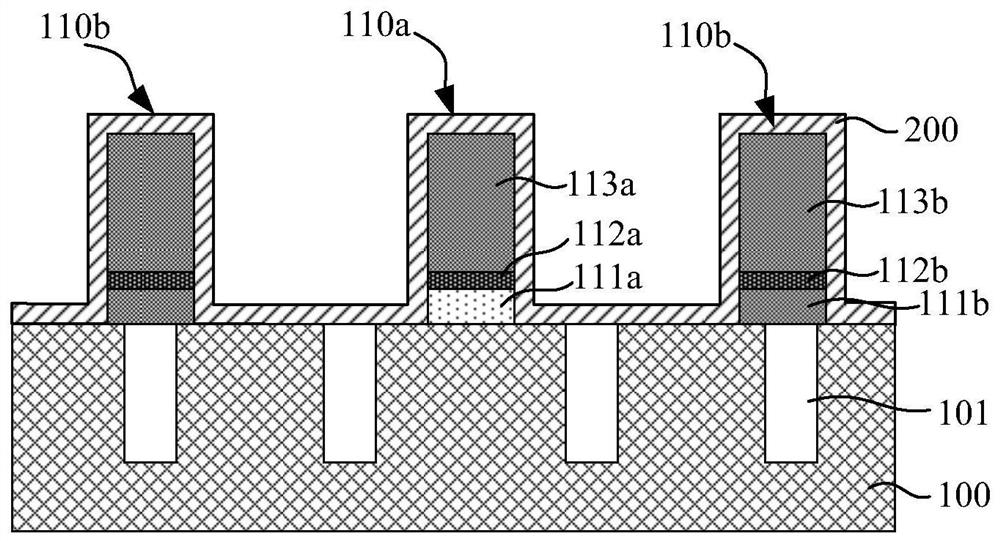

[0026] Please refer to Figure 1A and 1B 1. A substrate 100 is provided, and a plurality of bit line structures 110 arranged at intervals are formed on the substrate 100 . 1A is a schematic top view of the bit line structure 110 . Figure 1B for along Figure 1A Schematic cross-sectional view of the secant line AA'.

[0027] The semiconductor substrate 100 may include but not limited to a single crystal silicon substrate, a polycrystalline silicon substrate, a gallium nitride substrate or a sapphire substrate. In addition, when the semiconductor substrate 100 is a single crystal substrate or a polycrystalli...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More