Preparation method of three-dimensional broken line nanowire array vertical field effect transistor

A vertical field effect and line array technology, applied in the field of microelectronics, can solve the problems of high manufacturing cost, difficulty in obtaining, and low yield, and achieve the effects of improving current load and driving capability, wide application value, and increasing integration density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

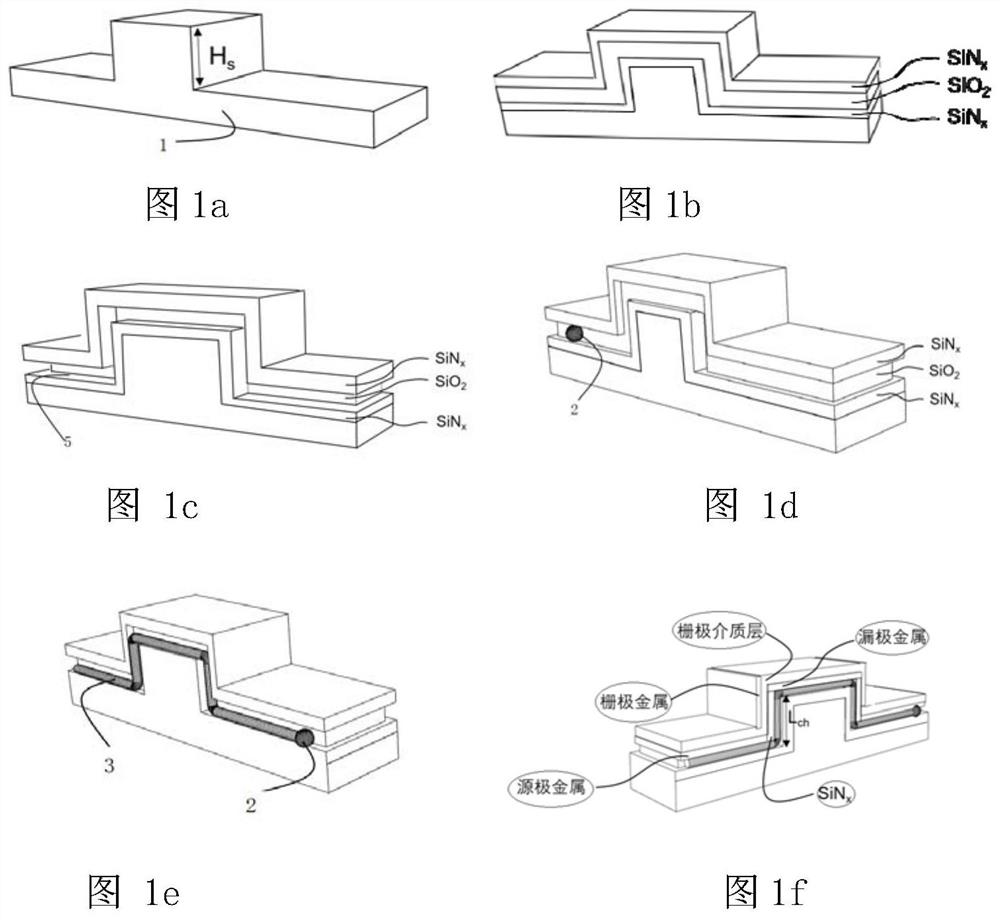

[0038] like figure 1 As shown, this embodiment provides a method for preparing a vertical gate transistor array by using a heterogeneous dielectric stack on a step to guide the growth of three-dimensional zigzag nanowires, which can be used to fabricate a vertical gate field effect transistor structure on a crystalline silicon substrate. The preparation process The following steps can be included:

[0039] 1) Use highly doped crystalline silicon as substrate 1, define the position of the guide step by photolithography, and then etch the surface of the substrate by ICP etching. The etching process uses C 4 F 8 and SF 6 Gas mixing 3:4 deep silicon etching technology to obtain vertical three-dimensional steps with a height of 200nm; such as figure 1 a shown.

[0040] 2) Alternately deposit amorphous silicon nitride-silicon oxide-silicon nitride films by plasma enhanced PECVD, the thickness of each film is 40-60-40nm respectively, and the heterogeneous dielectric stack is etc...

Embodiment 2

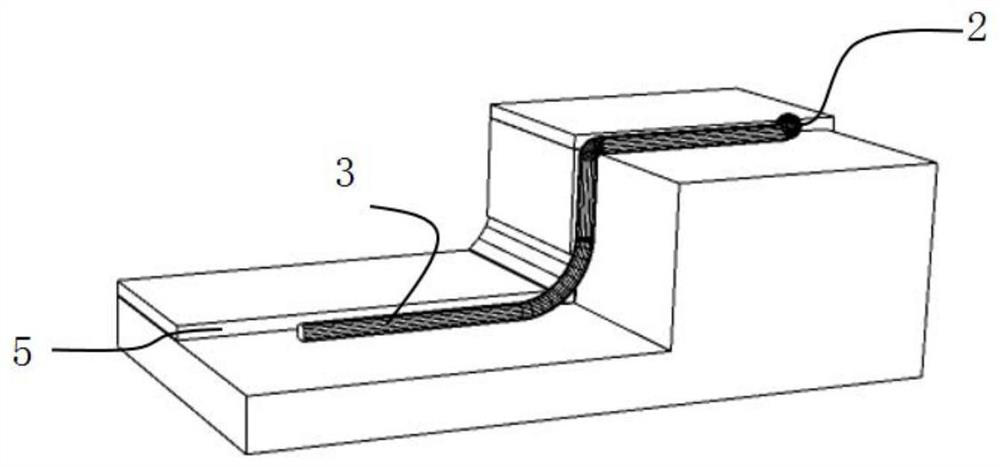

[0048] This embodiment provides a method for guiding the growth of single-layer three-dimensional zigzag nanowires by using a heterogeneous dielectric stack on a step, such as figure 2 shown, including the following steps:

[0049] 1) The shape of a single-layer three-dimensional step 5 is etched on the patterned substrate by etching technology;

[0050] 2) Deposit a homogeneous dielectric layer film on the etched substrate with three-dimensional steps, and use lithography to define the position and then etch to form a single-layer guide channel;

[0051] 3) preparing nano-scale catalytic metal particles 2 in the single-layer guiding channel;

[0052] 4) Deposit an amorphous semiconductor precursor film layer covering the desired growth nanowire on the entire surface of the structure;

[0053] 5) Raising the temperature makes the nano-scale catalytic metal particles change from solid state to liquid state in the single-layer guiding channel, the front end begins to absorb t...

Embodiment 3

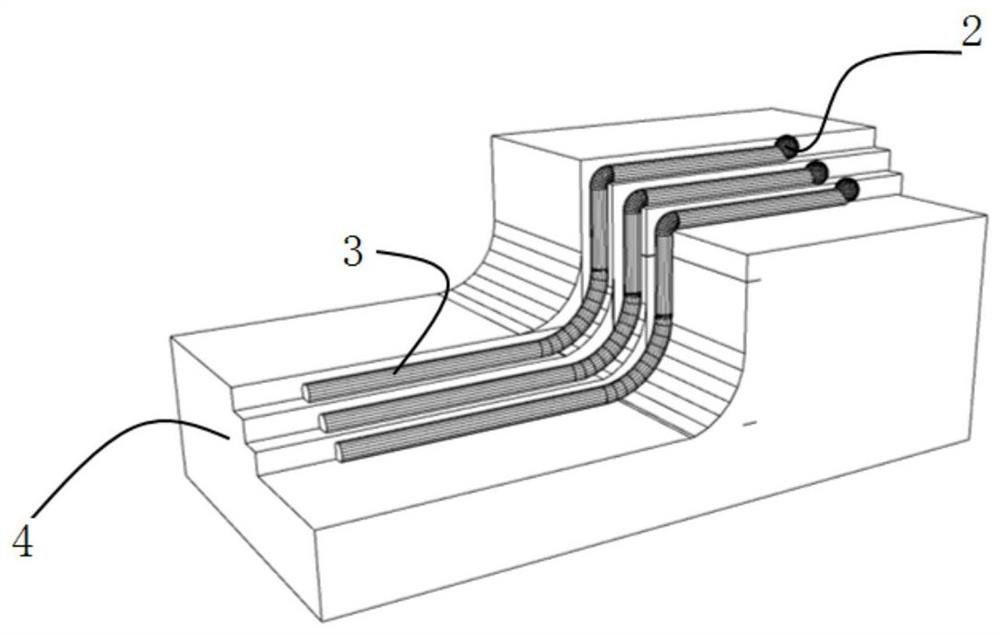

[0056] This embodiment provides a method for guiding the growth of multi-layer three-dimensional zigzag nanowires by using a heterogeneous dielectric stack on a step, such as image 3 shown, including the following steps:

[0057] 1) Using etching technology to etch the shape of multi-layer three-dimensional steps 4 on the patterned substrate;

[0058] 2) Deposit a film of a heterogeneous dielectric layer on a substrate etched with three-dimensional steps, and use lithography to define the position and then etch to form a multi-layer guide channel;

[0059] 3) preparing nano-scale catalytic metal particles 2 in the multi-layer guiding channel;

[0060] 4) Deposit an amorphous semiconductor precursor film layer covering the desired growth nanowire on the entire surface of the structure;

[0061] 5) Raising the temperature makes the nano-scale catalytic metal particles change from solid state to liquid state in the multi-layer guiding channel, the front end begins to absorb th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com